# **Computer Organization**

# Unit 2. Machine Instructions and Programs 13.12.17

Topics covered:

Course outline and schedule

Introduction

Dr e v prasad

# Chapter 2. Machine Instructions and Programs

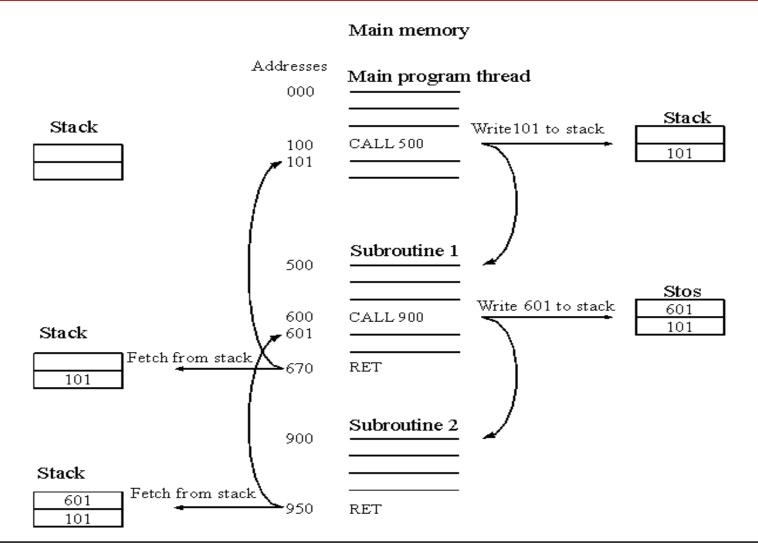

- > Machine instructions and program execution, including branching and subroutine call and return operations.

- > Number representation and addition/subtraction in the 2's-complement system.

- > Addressing methods for accessing register and memory operands.

- > Assembly language for representing machine instructions, data, and programs.

- Program-controlled Input/output operations.

# Number, Arithmetic Operations, and Characters

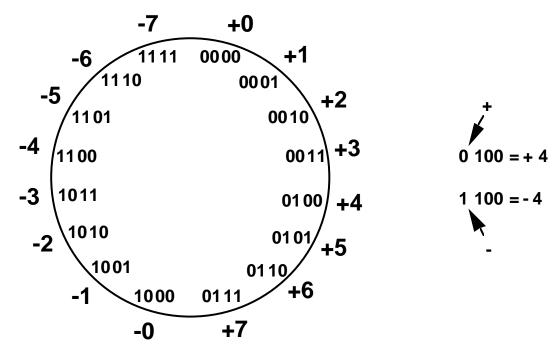

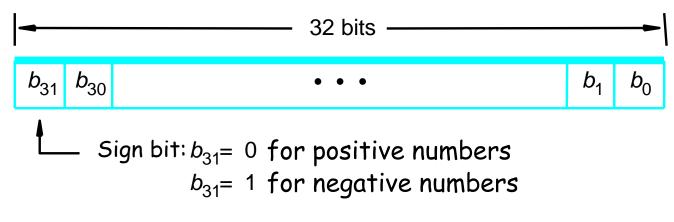

## Signed Integer

> 3 major representations:

Sign and magnitude

One's complement

Two's complement

> Assumptions:

4-bit machine word

16 different values can be represented

Roughly half are positive, half are negative

#### Sign and Magnitude Representation

- → High order bit is sign: 0 = positive (or zero), 1 = negative

→ Three low order bits is the magnitude:

- - 0 (000) thru 7 (111)

- > Number range for n bits = (+/-) 2<sup>n-1</sup> -1

- >Two representations for O

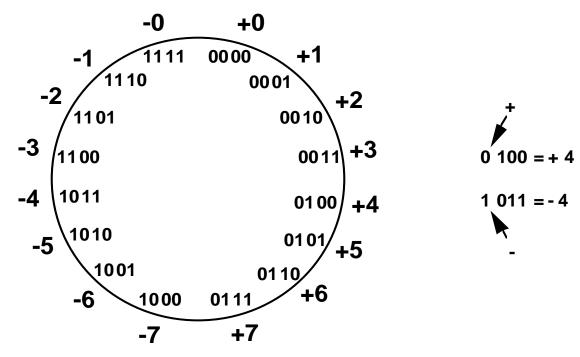

### One's Complement Representation

- > Subtraction implemented by addition & 1's complement

- > Still two representations of 0! This causes some problems

- > Some complexities in addition perform binary addition, then add in an end-around carry value.

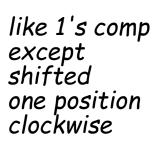

#### Two's Complement Representation

- > Only one representation for 0

- > One more negative number than positive number

# Binary, Signed-Integer Representations

| В                                                                                                                   | Values represented                                      |                                                                                  |                                                         |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------|

| $b_3^{} b_2^{} b_1^{} b_0^{}$                                                                                       | Sign and<br>magnitude                                   | 1's complement                                                                   | 2's complement                                          |

| 0 1 1 1<br>0 1 0<br>0 1 0 1<br>0 1 0 0<br>0 0 1 1<br>0 0 0 0<br>1 0 0 0<br>1 0 0 0<br>1 0 1 1<br>1 0 1 0<br>1 1 0 1 | + 7 + 6 + 5 + 4 + 3 + 2 + 1 + 0 - 0 - 1 - 2 - 3 - 4 - 5 | +7<br>+6<br>+5<br>+4<br>+3<br>+2<br>+1<br>+0<br>-7<br>-6<br>-5<br>-4<br>-3<br>-2 | + 7 + 6 + 5 + 4 + 3 + 2 + 1 + 0 - 8 - 7 - 6 - 5 - 4 - 3 |

| 1 1 1 0 1 1 1                                                                                                       | - 6<br>- 7                                              | - 1<br>- 0                                                                       | - 2<br>- 1                                              |

Figure 2.1. Binary, signed-integer representations.

# Addition and Subtraction - 2's Complement

|                                                           | 4          | 0100        | -4            | 1100  |

|-----------------------------------------------------------|------------|-------------|---------------|-------|

| If conny in to the high                                   | <u>+ 3</u> | 0011        | + <u>(-3)</u> | 1101  |

| If carry-in to the high order bit = carry-out then ignore | 7          | 0111        | -7            | 11001 |

| carry                                                     |            |             |               |       |

| if carry-in differs from carry-out then overflow          | 4          | 0100        | -4            | 1100  |

|                                                           | 3          | <u>1101</u> | <u>+ 3</u>    | 0011  |

|                                                           | 1          | 10001       | -1            | 1111  |

|                                                           |            | L           |               |       |

Simpler addition scheme makes twos complement the most common choice for integer number systems within digital systems

#### 2's-Complement Add and Subtract Operations

Figure 2.4. 2's-complement Add and Subtract operations.

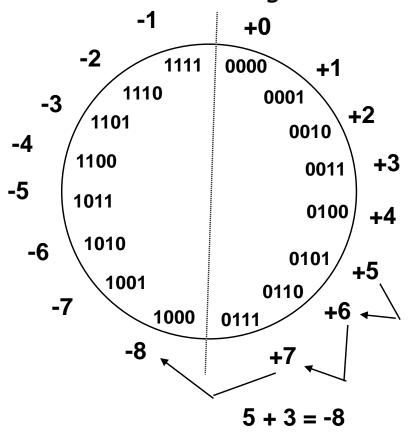

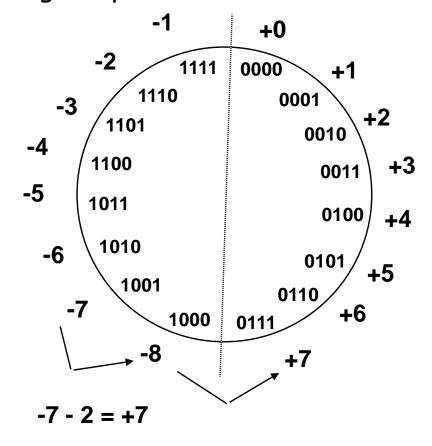

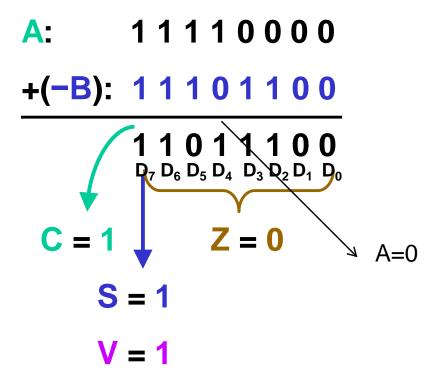

#### Overflow in 2's-Complement Addition

Overflow - Add two positive numbers to get a negative number or two negative numbers to get a positive number

| 5           | 0 1 1 1<br>0 1 0 1 | -7        | $\begin{array}{c} 1 \ 0 \ 0 \ 0 \\ 1 \ 0 \ 0 \ 1 \end{array}$ |

|-------------|--------------------|-----------|---------------------------------------------------------------|

| _3_         | 0011               | <u>-2</u> | 1100                                                          |

| -8          | 1000               | 7         | 1 <sub> </sub> 0 1 1 1                                        |

| Overflow    |                    | Overflo   | )W                                                            |

| 5           | 0 0 0 0<br>0 1 0 1 | -3        | 1 1 1 1<br>1 1 0 1                                            |

| _2_         | 0010               | <u>-5</u> | 1011                                                          |

| 7           | 0111               | -8        | 1 1 0 0 0                                                     |

| No overflow |                    | No over   | flow                                                          |

Overflow when carry-in to the high-order bit does not equal carry out

# 2's-Complement Addition-examples 1

| $   \begin{array}{r}     1001 = -7 \\     +0101 = 5 \\     1110 = -2 \\     (a) (-7) + (+5)   \end{array} $ | 1100 = -4  +0100 = 4  10000 = 0  (b) (-4) + (+4)              |

|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 0011 = 3 + 0100 = 4 0111 = 7 (c) (+3) + (+4)                                                                | 1100 = -4  + 1111 = -1  11011 = -5  (d) (-4) + (-1)           |

| 0101 = 5  + 0100 = 4  1001 = Overflow  (e) (+5) + (+4)                                                      | 1001 = -7<br>+1010 = -6<br>10011 = Overflow<br>(f)(-7) + (-6) |

# 2's-Complement Addition-examples 2

| 0010 = 2                     | 0101 = 5           |

|------------------------------|--------------------|

| +1001 = -7                   | +1110 = -2         |

| $\overline{1011} = -5$       | 10011 = 3          |

| (a) $M = 2 = 0010$           | (b) $M = 5 = 0101$ |

| S = 7 = 0111                 | S = 2 = 0010       |

| -s = 1001                    | -s = 1110          |

| 1011 = -5                    | 0101 = 5           |

| +1110 = -2                   | +0010 = 2          |

| 11001 = -7                   | 0111 = 7           |

| (c) $M = -5 = 1011$          | (d) $M = 5 = 0101$ |

| S = 2 = 0010                 | S = -2 = 1110      |

| -s = 1110                    | -s = 0010          |

| 0111 = 7                     | 1010 = -6          |

| +0111 = 7                    | +1100 = -4         |

| $\overline{1110}$ = Overflow | 10110 = Overflow   |

| (e) $M = 7 = 0111$           | (f) M = -6 = 1010  |

| S = -7 = 1001                | s = 4 = 0100       |

| -s = 0111                    | -S = 1100          |

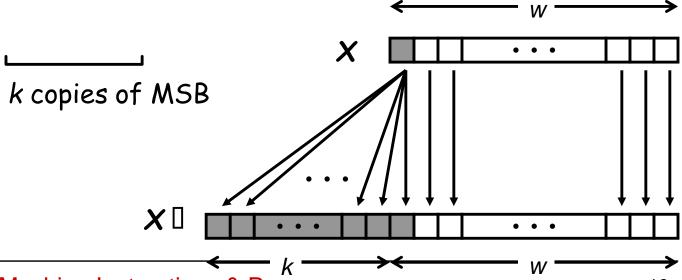

### Sign Extension

- ☐ Task:

- ◆ Given w-bit signed integer x

- $\bullet$  Convert it to w+k-bit integer with same value

- ☐ Rule:

- ◆ Make k copies of sign bit:

- $A \times \Box = x_{w-1}, ..., x_{w-1}, x_{w-1}, x_{w-2}, ..., x_0$

# Sign Extension Example

```

short int x = 15213;

int ix = (int) x;

short int y = -15213;

int iy = (int) y;

```

|    | Decimal | Hex         | Binary                              |

|----|---------|-------------|-------------------------------------|

| X  | 15213   | 3B 6D       | 00111011 01101101                   |

| ix | 15213   | 00 00 C4 92 | 00000000 00000000 00111011 01101101 |

| У  | -15213  | C4 93       | 11000100 10010011                   |

| iy | -15213  | FF FF C4 93 | 11111111 11111111 11000100 10010011 |

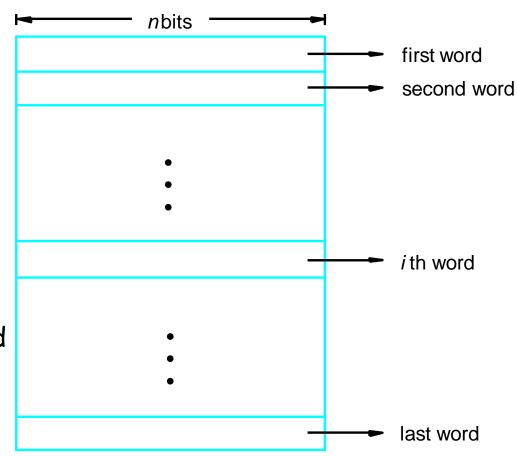

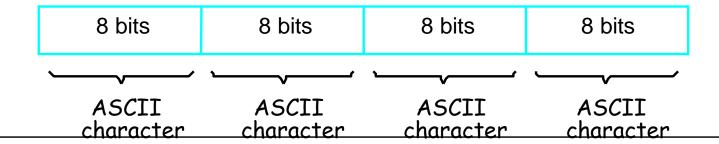

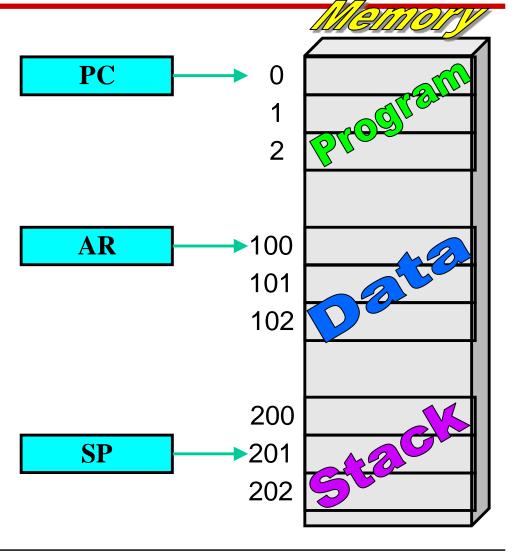

Memory consists of many millions of storage cells, each of which can store 1 bit.

Data is usually accessed in n-bit groups. n is called word length.

Figure 2.5. Memory words.

☐ 32-bit word length example

(a) A signed integer

(b) Four characters

- > To retrieve information from memory, either for one word or one byte (8-bit), addresses for each location are needed.

- $\triangleright$  A k-bit address memory has  $2^k$  memory locations, namely 0 to  $(2^k-1)$ , called memory space.

- $\gt$  24-bit memory:  $2^{24} = 16,777,216 = 16M (1M=2^{20})$

- > 32-bit memory:  $2^{32} = 4G (1G=2^{30})$

- > 1K (kilo)=2<sup>10</sup>

- > 1T (tera)=2<sup>40</sup>

- $\rightarrow$  1P (peta)=2<sup>50</sup>

- > It is impractical to assign distinct addresses to individual bit locations in the memory.

- The most practical assignment is to have successive addresses refer to successive byte locations in the memory byte-addressable memory.

- > Byte locations have addresses 0, 1, 2, ... If word length is 32 bits, they successive words are located at addresses 0, 4, 8,...

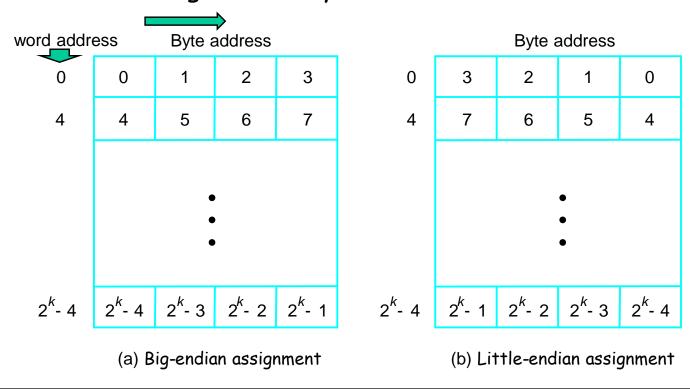

### Big-Endian and Little-Endian Assignments

Big-Endian: lower byte addresses are used for the most significant bytes of the word

Little-Endian: opposite ordering. lower byte addresses are used for the less significant bytes of the word

Figure 2.7. Byte and word addressing.

- > Address ordering of bytes

- Word alignment

- ♦ Words are said to be aligned in memory if they begin at a byte addr. that is a multiple of the num of bytes in a word.

- 16-bit word: word addresses: 0, 2, 4,....

- 32-bit word: word addresses: 0, 4, 8,....

- 64-bit word: word addresses: 0, 8, 16,....

- > Access numbers, characters, and character strings

#### **Memory Operation**

- Load (or Read or Fetch)

- > Copy the content. The memory content doesn't change.

- Address Load

- Registers can be used

- ☐ Store (or Write)

- > Overwrite the content in memory

- > Address and Data Store

- Registers can be used

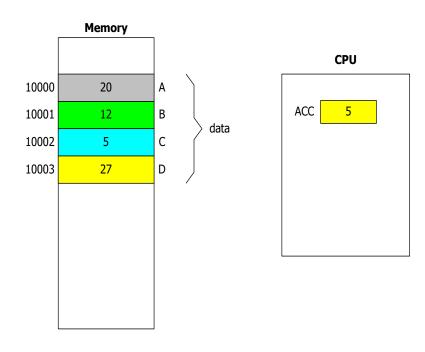

## Instructions and Instruction Sequencing

## "Must-Perform" Operations

- > Task carried out by a computer program consists of a sequence of small steps:

- > Data transfers between the memory and the processor registers

Load and store

- Arithmetic and logic operations on data adding two numbers, complementing a number

- Program sequencing and control testing a particular condition ,transfer control

- I/O transfers

Reading a character from the key board

Sending a character to be displayed on a display screen

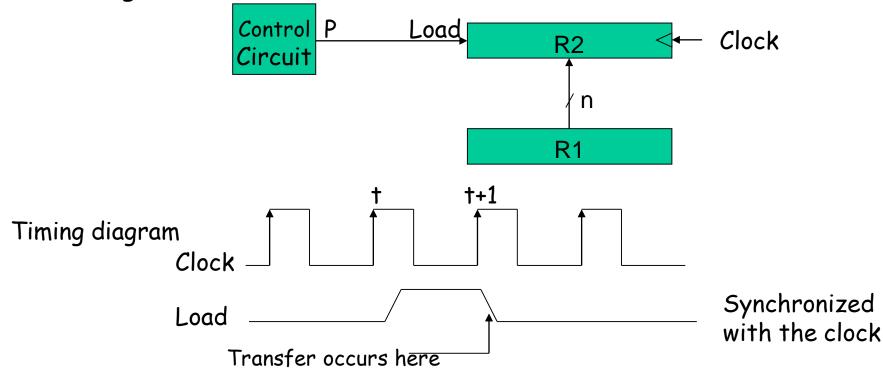

## Register Transfer Notation

- ☐ A symbolic notation to describe the microoperation transfers among registers.

- register transfer language (RTL) is a kind of intermediate representation (IR) that is very close to assembly language, such as that which is used in a compiler.

- It is used to describe data flow at the registertransfer level of an architecture.

- ➤ Identify a location by a symbolic name standing for its hardware binary address (LOC, RO,...)

- > Contents of a location are denoted by placing square brackets around the name of the location

$$(R1\leftarrow[LOC], R3\leftarrow[R1]+[R2])$$

- □ Representation of a (conditional) transfer

- P:  $R2 \leftarrow R1$

- Register Transfer Notation (RTN)

#### Register Transfer

Hardware implementation of a controlled transfer:  $P: R2 \leftarrow R1$

Block diagram:

# Assembly Language Notation

- > Represent machine instructions and programs.

- $\triangleright$  Move LOC, R1 = R1 $\leftarrow$ [LOC]

- $\triangleright$  Add R1, R2, R3 = R3 ←[R1]+[R2]

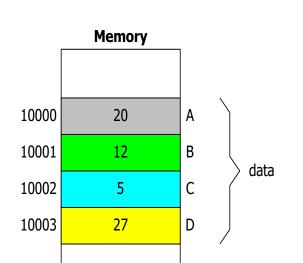

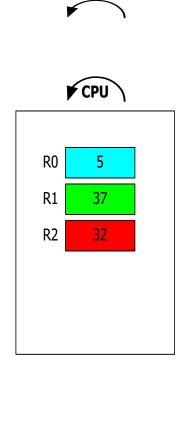

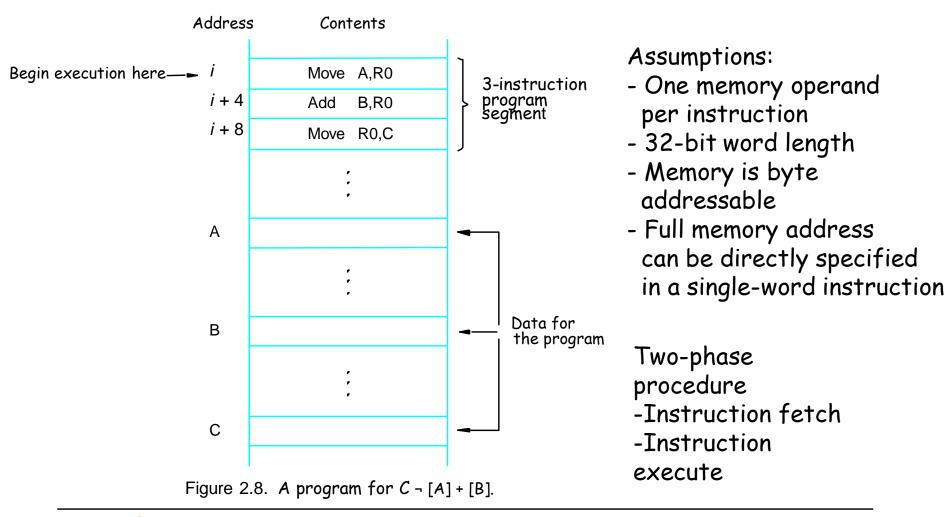

## CPU Organization

- Single Accumulator

- > Result usually goes to the Accumulator

- > Accumulator has to be saved to memory quite often

- > General Register

- > Registers hold operands thus reduce memory traffic

- Register bookkeeping

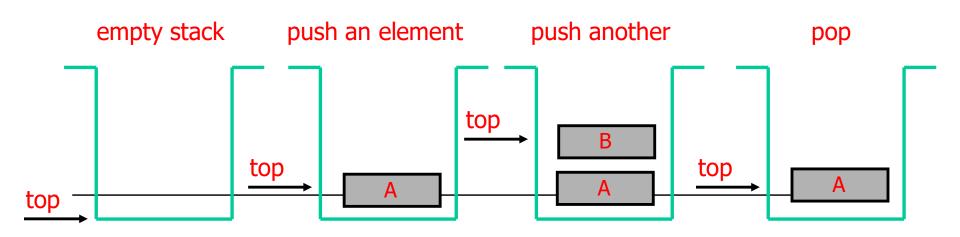

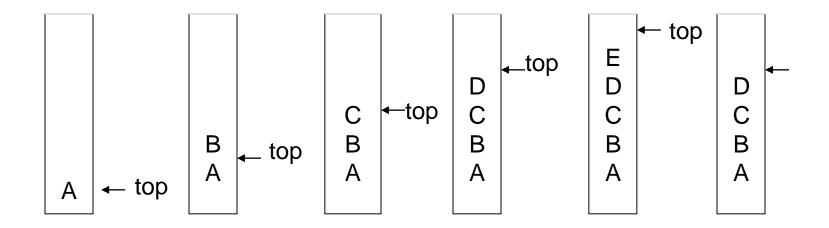

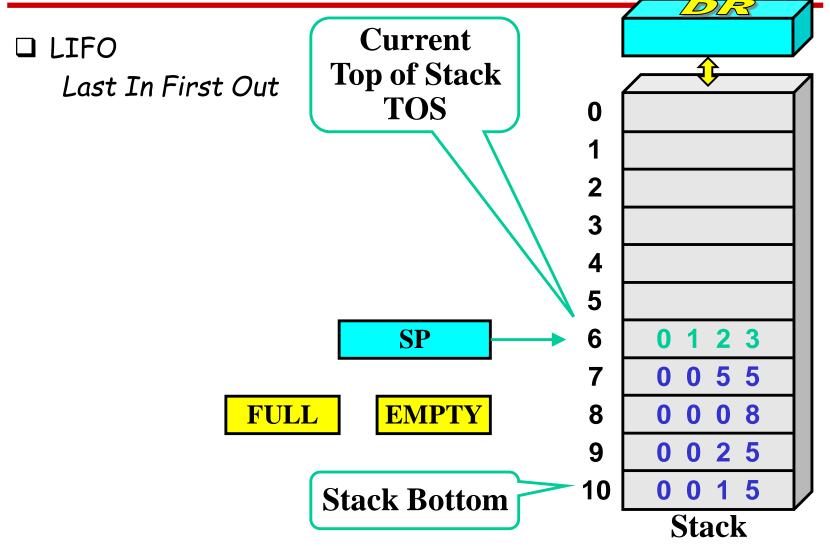

- > Stack

- > Operands and result are always in the stack

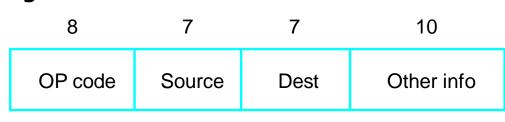

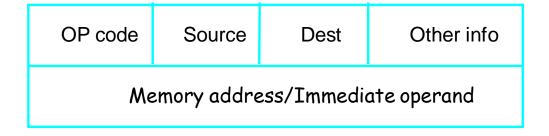

#### **Instruction Formats**

- > Three-Address Instructions

- > ADD R1, R2, R3

$R1 \leftarrow R2 + R3$

- > Two-Address Instructions

- > ADD R1, R2

$R1 \leftarrow R1 + R2$

- One-Address Instructions

- > ADD M

$AC \leftarrow AC + M[AR]$

- Zero-Address Instructions

- > ADD

$TOS \leftarrow TOS + (TOS - 1)$

- > RISC Instructions

- > Lots of registers.

- Memory is restricted to Load & Store

#### three address instruction

- > Three explicit operands per instruction

- Operands specify source, destination, and result

- Directly operate on memory variables or registers

- Use Temp variables

- > Operations are with the memory variables/two (one) memory variable(s) Note: ADD R2,R0,R1 means R2 = R0+R1and one (two) register(s)

D = A + B + C

#### two address instruction

- Two explicit operands per instruction

- Result overwrites one of the operands

- Operands known as source and destination

- Works well for instructions such as memory copy

- Uses Move (MOV) instruction

- MOV instruction transfers the operands between memory and processor registers

- Operations are in the registers / one in register

D = A + B + CMemory **CPU** 10000 20 5 12 В 10001 data 37 10002 32 10003 27 D

Note: ADD RO,R1 means RO = RO+R1

#### One address instruction

- One explicit operand per instruction

- Second operand is implicit

Always found in hardware register Known as accumulator (reg A)

- > AC contains the result of all operations.

- Uses Load (LDA) and Store (STA) to access memory

- Operations are in the registers/ one can be in memory

Note: ADD [10001] means <math>Acc = Acc + [10001]

## **Instruction Formats**

Example: Evaluate (A+B) \* (C+D)

☐ Three-Address

```

1. ADD

R1, A, B

; R1 \leftarrow M[A] + M[B]

2. ADD

R2, C, D

; R2 \leftarrow M[C] + M[D]

3. MUL

X, R1, R2

; M[X] \leftarrow R1 * R2

```

- > Three-address instruction formats can use each address field to specify either a processor register or a memory operand.

- It is assumed that the computer has two processor registers, R1 and R2. The symbol M [X] denotes the operand at memory address symbolized by A.

- The advantage of the three-address format is that it results in short programs when evaluating arithmetic expressions.

- The disadvantage is that the binary-coded instructions require too many bits to specify three addresses.

Example: Evaluate (A+B) \* (C+D)

#### ☐ Two-Address

6. MOV

```

1. MOV

R1, A

; R1 \leftarrow M[A]

2. ADD

R1, B

; R1 \leftarrow R1 + M[B]

3. MOV

R2, C

; R2 \leftarrow M[C]

4. ADD

R2, D

; R2 \leftarrow R2 + M[D]

5. MUL

R1, R2

; R1 \leftarrow R1 * R2

```

- each address field can specify either a processor register or a memory word.

- > MOV instruction moves or transfers the operands to and from memory and processor registers.

$M[X] \leftarrow R1$

The first symbol listed in an instruction is assumed to be both a source and the destination

X, R1

Example: Evaluate (A+B) \* (C+D)

#### One-Address

- 1. LOAD A

- 2. ADD B ;  $AC \leftarrow AC + M[B]$

$AC \leftarrow M[A]$

- 3. STORE T ;  $M[T] \leftarrow AC$

- 4. LOAD C ;  $AC \leftarrow M[C]$

- 5. ADD D ;  $AC \leftarrow AC + M[D]$

- 6. MUL T ;  $AC \leftarrow AC * M[T]$

- 7. STORE X ;  $M[X] \leftarrow AC$

- One-address instructions use an implied accumulator (AC) register for all data manipulation.

- All operations are done between the AC register and a memory operand

- Uses LOAD and STORE instructions to transfer the operands between memory and processor registers.

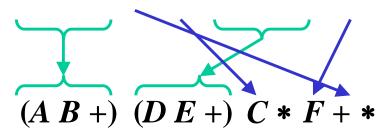

Example: Evaluate (A+B) \* (C+D)

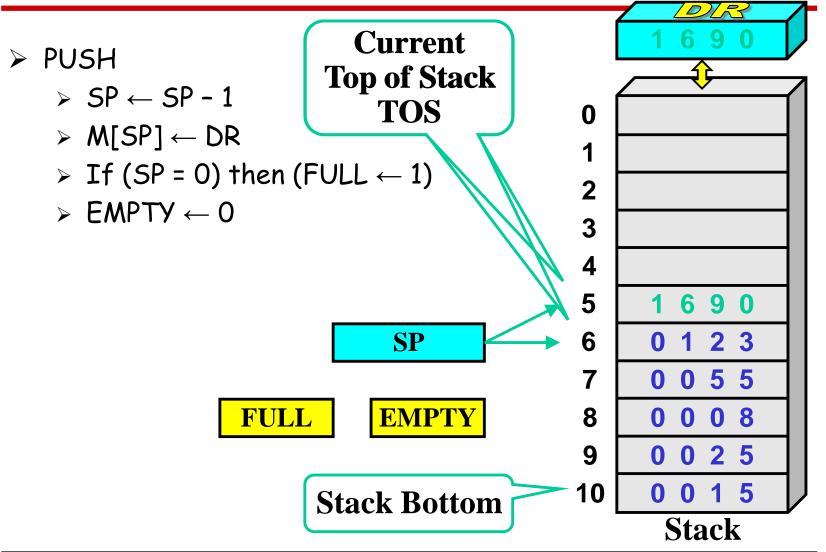

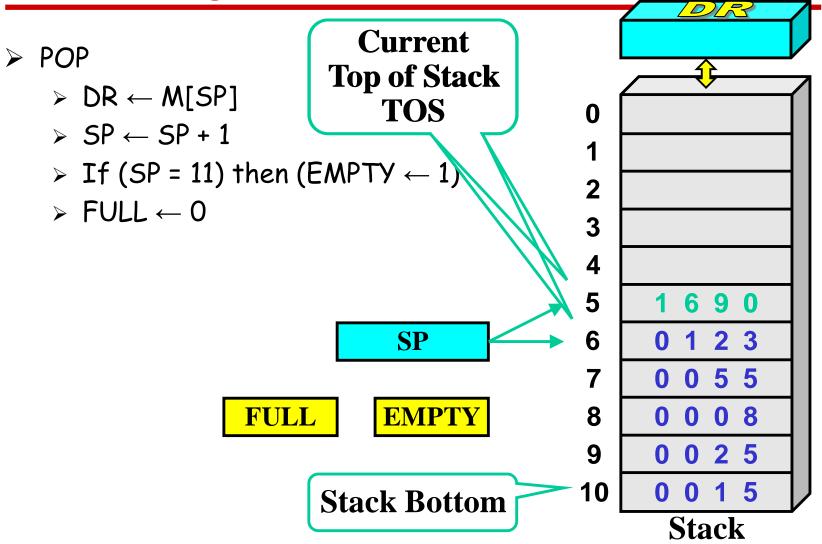

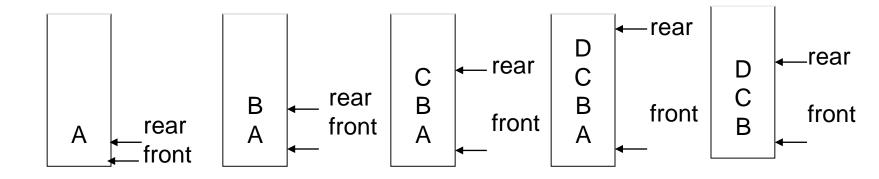

#### □ Zero-Address

- 1. PUSH A ; TOS  $\leftarrow$  A

- 2. PUSH B ;  $TOS \leftarrow B$

- 3. ADD ;  $TOS \leftarrow (A + B)$

- 4. PUSH C ; TOS  $\leftarrow C$

- 5. PUSH D ;  $TOS \leftarrow D$

- 6. ADD ;  $TOS \leftarrow (C + D)$

- 7. MUL ;  $TOS \leftarrow (C+D)*(A+B)$

- 8. POP X ;  $M[X] \leftarrow TOS$

- A stack-organized computer does not use an address field for the instructions ADD and MUL.

- > The PUSH and POP instructions, need an address field to specify the operand that communicates with the stack.

Example: Evaluate (A+B) \* (C+D)

#### □ RISC

```

1. LOAD R1, A ; R1 \leftarrow M[A]

```

2. LOAD R2, B ; R2

$$\leftarrow$$

M[B]

3. LOAD R3, C ; R3

$$\leftarrow$$

M[C]

4. LOAD R4, D ; R4

$$\leftarrow$$

M[D]

5. ADD R1, R1, R2 ; R1

$$\leftarrow$$

R1 + R2

6. ADD R3, R3, R4 ; R3

$$\leftarrow$$

R3 + R4

7. MUL R1, R1, R3 ; R1

$$\leftarrow$$

R1  $*$  R3

8. STORE X, R1 ;

$$M[X] \leftarrow R1$$

- Uses registers fro all operations

- Uses LOAD and STORE instructions for operand transfer.

# Practice on the following expression $Y=(A-B)/(C+D \times E)$

## Example: $Y=(A-B)/(C+D \times E)$

| <u>Three</u>   | Two Address | ses               |

|----------------|-------------|-------------------|

| Addresses:     | MOVY, A     |                   |

| SUBY, A, B     | SUBY, B     |                   |

| MPY T, D, E    | MOV T, D    |                   |

| ADD T, T, C    | MPY T,E     |                   |

| DIV Y, Y, T    | ADD T,C     | Stack (O address) |

| •              | DIV Y, T    | Push A            |

| One Addresses: | •           | Push B            |

| LOADD          |             | SUB               |

| MPY E          |             | Push C            |

| ADD C          |             | Push D            |

| STOR Y         |             | Push E            |

| LOAD A         |             | MPY               |

| SUB B          |             | ADD               |

| DIVY           |             | DIV               |

|                |             | Pop Y             |

## Using Registers

- > Registers are faster

- > Shorter instructions

- > The number of registers is smaller (e.g. 32 registers need 5 bits)

- Potential speedup

- Minimize the frequency with which data is moved back and forth between the memory and processor registers.

#### Instruction Execution and Straight-Line Sequencing

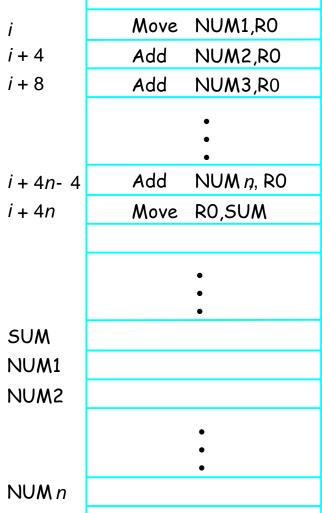

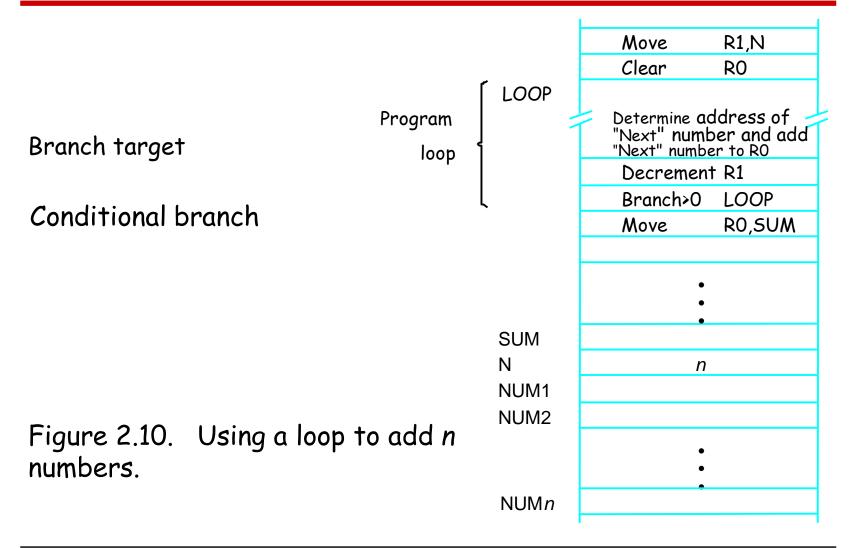

Figure 2.9. A straight-line program for adding n numbers.

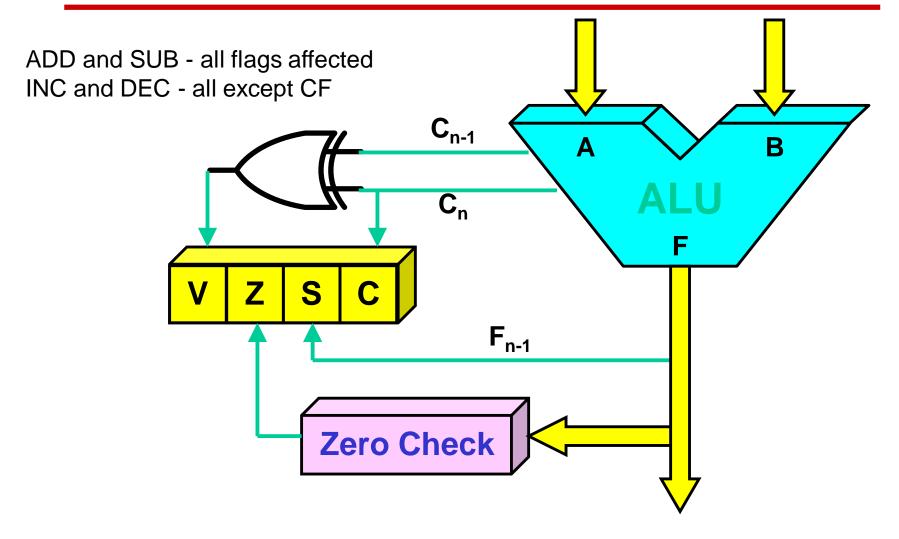

Status flags (CF, PF, AF, ZF, SF, OF)

Set to represent the result of certain operations

Used to control conditional jump instructions

Different instructions affect different flags

- Condition code flags

- N /SF (negative/sign)

- > ZF (zero)

- > VF (overflow)

- > CF (carry)

- PF (Parity Flag)

- > AF (Auxiliary Flag)

- Condition code register / status register

## Condition Codes/Flags

#### Status Flags

Carry (CF): carry or borrow at MSB in add or subtract

last bit shifted out

Parity (PF): low byte of result has even parity (PF)

Auxiliary (AF): carry or borrow at bit 3

Zero (ZF): result is 0

Sign (SF): result is negative

Overflow (OF/VF): signed overflow occurred during add or subtract

1) CF = 1 if there is a carry out from the MSB on addition, or there is a borrow into the MSB on subtraction

CF = 0 otherwise

CF is also affected by shift and rotate instructions

- 2) PF = 1 if the low byte of a result has an even number of ones (even parity) PF = 0 otherwise (odd parity)

- 3) AF = 1 if there is a carry out from bit 3 on addition, or there is a borrow into the bit 3 on subtraction

AF = 0 otherwise

AF is used in binary-coded decimal (BCD) operations.

4) ZF = 1 for a zero result

ZF = 0 for a non-zero result

5) SF = 1 if the MSB of a result is 1; it means the result is negative if you are giving a signed interpretation

SF = 0 if the MSB is 0

6) OF/VF = 1 if signed overflow occurred OF/VF = 0 otherwise

(Signed) Overflow Can only occur when adding numbers of the same sign (subtracting with different signs)

Detected when carry into MSB is not equal to carry out of MSB Easily detected because this implies the result has a different sign than the sign of the operands.

Programs can ignore the Flags!

## Signed Overflow (Example)

#### **Example 1**

```

10010110

+ 10100011

00111001

Carry in = 0, Carry out = 1

Neg+Neg=Pos

Signed overflow occurred: OF/VF= 1 (set)

Example 2

00110110

+ 01100011

10011001

Carry in = 1, Carry out = 0

Pos+Pos=Neg

Signed overflow occurred: OF/VF = 1 (set)

```

#### Examples of No Signed Overflow

#### Example 3

```

10010110

+ 01100011

11111001

Carry in = 0, Carry out = 0

Neg+Pos=Neg

No Signed overflow occurred: OF /VF= 0 (clear)

Example 4

10010110

+ 11110011

10001001

Carry in = 1, Carry out = 1

Neg+Neg=Neg

No Signed overflow occurred: OF /VF= 0 (clear)

```

## Unsigned Overflow (Example)

#### Example 5

The carry flag is used to indicate if an unsigned operation overflowed

•The processor only adds or subtracts - it does not care if the data is signed or unsigned!

```

10010110

```

+ 11110011 10001001

Carry out = 1

Unsigned overflow occurred : CF = 1 (set)

#### Conditional Branch Instructions

- ☐ Example:

- ◆ A: 11110000

- ◆ B: 00010100

#### Status Bits

The different ways in which the operand address (registers/memory) is specified in an instruction are referred to as addressing modes.

Why use of use addressing mode techniques?

- > To give programming versatility to the user by providing such facilities as pointers to Memory, counters for loop control, indexing of data, and program relocation.

- To reduce the number of bits in the addressing field of the instruction.

- > The availability of the addressing modes gives the experienced assembly language programmer flexibility for writing programs that are more efficient with respect to the number of instructions and execution time.

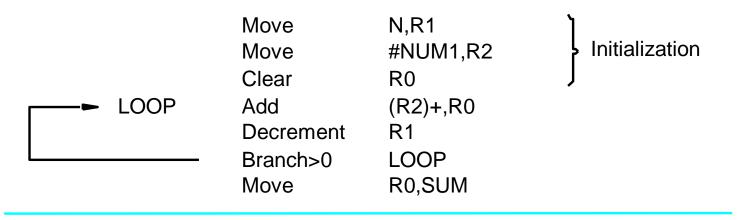

## Generating Memory Addresses

- How to specify the address of branch target?

- Can we give the memory operand address directly in a single Add instruction in the loop?

- Use a register to hold the address of NUM1; then increment by 4 on each pass through the loop.

- > Implied

- > AC is implied in "ADD M[AR]" in "One-Address" instr.

- > TOS is implied in "ADD" in "Zero-Address" instr.

- > Immediate

- The operand is given explicitly in the instruction

- > The use of a constant in "MOV R1, 5", i.e. R1  $\leftarrow$  5

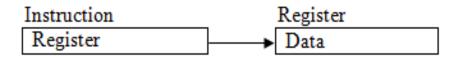

- > Register

- > Indicate which register holds the operand

- > The operand is the contents of a processor register; the name

- address) of the register is given in the instruction.

- Effective address (EA) = R

- MOV R1, R2

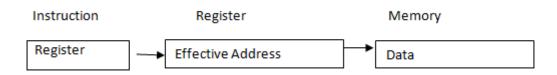

- ☐ Register Indirect

- ◆ Indicate the register that holds the number of the register that holds the operand

MOV R1, (R2) or MOV R1, (LOC)

R2 = 300

- ☐ Autoincrement / Autodecrement

- ◆ Access & update in 1 instr.

- ☐ Direct Address (ABSOLUTE MODE)

- ♦ Use the given address to access a

- memory location.

Effective address (EA) = address field (A)

The operand is in a memory location;

the address of this location is given explicitly in the instruction

e.g. ADD A

300

#### ☐ Indirect Address

The effective address of the operand is the contents of a register or memory location whose address appears in the instruction.

> Indicate the memory location that holds the address of the memory location that holds the data

- > The register or memo AR = 101

- > location that contains the address of an

- > operand is called a pointer.

- > EA= pointer

- $\succ$  EA = (A)

## 1. Immediate Addressing Mode

The operand is specified with in the instruction.

Operand itself is provided in the instruction rather than its address

Instruction

Move Immediate

Data

MVIA, 15h;  $A \leftarrow 15H$ ; 15 h is the immediate operand

Add Immediate

**ADI 3Eh**;  $A \leftarrow A + 3EH$ ; 3Eh is the immediate operand

## 2. Register Addressing Mode

The operand is specified with in one of the processor registers.

Instruction specifies the register in which the operand is stored.

#### Move

MOVC, A;  $C \leftarrow A$  Here A is the operand specified

Add

**ADD** B;

$$A \leftarrow A + B$$

## 3. Register Indirect Addressing Mode

The instruction specifies the register in which the memory address of operand is placed.

$$MOVA$$

,  $M$  Move  $A \leftarrow [[H][L]]$

It moves the data from memory location specified by HL register pair to A

#### EX 1. Register Indirect Addressing Mode

MOV A, M

$$A \leftarrow [[H][L]]$$

It moves the data from memory location specified by HL register pair to A.

Before After **A9 A9 A9** H H  $A \leftarrow A9$  $A \leftarrow [2805]$

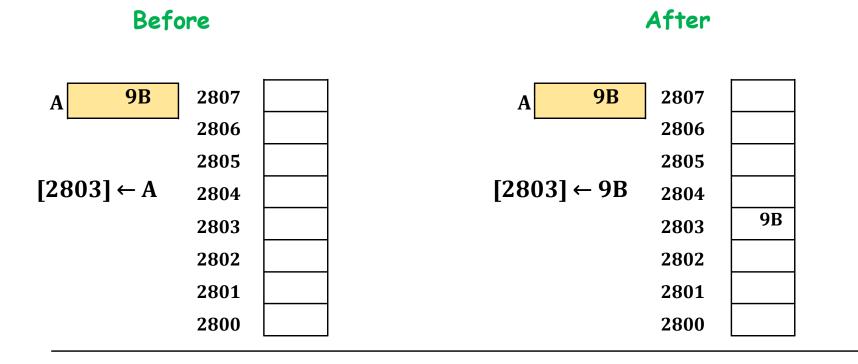

## 4. Direct Addressing Mode

The instruction specifies the direct address of the operand.

The memory address is specified where the actual operand is.

#### Load Accumulator

**LDA 2805h**

$$A \leftarrow [2805]$$

It loads the data from memory location 2805 to A.

#### Store Accumulator

**STA 2803h**  $[2803] \leftarrow A$

It stores the data from A to memory location 2803.

## Ex 1. Direct Addressing Mode

LDA 2805 H

$$A \leftarrow [2805]$$

It loads the data from the memory location 2805 H to A

**Before** After

| A          | 2807 |    | A 5C                 | 2807 |    |

|------------|------|----|----------------------|------|----|

| A ← [2805] | 2806 |    |                      | 2806 |    |

|            | 2805 | 5C |                      | 2805 | 5C |

|            | 2804 |    | <b>A</b> ← <b>5C</b> | 2804 |    |

|            | 2803 |    |                      | 2803 |    |

|            | 2802 |    |                      | 2802 |    |

|            | 2801 |    |                      | 2801 |    |

|            | 2800 |    |                      | 2800 |    |

## Ex 2. Direct Addressing Mode

**STA 2803h**

$$[2803] \leftarrow A$$

It copies the data stored in Register A in memory location 2803.

## 5. Indirect Addressing Mode

The instruction specifies the indirect address where the effective address of the operand is placed.

The memory address is specified where the actual address of operand is placed.

**MOV A, 2802 H**;

$$A \leftarrow [[2802]]$$

It moves the data from memory location specified by the location 2802 to A.

## Ex. Indirect Addressing Mode

**MOV A, [2802]h**

$$A \leftarrow [[280 2]]$$

$$A \leftarrow [[280\ 2]]$$

It transfer the data from memory specified memory location to A

**Before After**

| A            | 2807 |    | A FF              | 2807 |    |

|--------------|------|----|-------------------|------|----|

|              | 2806 | FF |                   | 2806 | FF |

|              | 2805 |    |                   | 2805 |    |

| A ← [[2806]] | 2804 |    | $A \leftarrow FF$ | 2804 |    |

|              | 2803 | 06 |                   | 2803 | 06 |

|              | 2802 | 28 |                   | 2802 | 28 |

|              | 2801 |    |                   | 2801 |    |

|              | 2800 |    |                   | 2800 |    |

## 6.

## 6. Implied Addressing Mode

It is also called inherent addressing mode.

The operand is implied by the instruction.

The operand is hidden/fixed inside the instruction.

Complement Accumulator : CMA

(Here accumulator A is implied by the instruction)

Complement Carry Flag: CMC

(Here Flags register is implied by the instruction)

Set Carry Flag: STC

# **\langle**

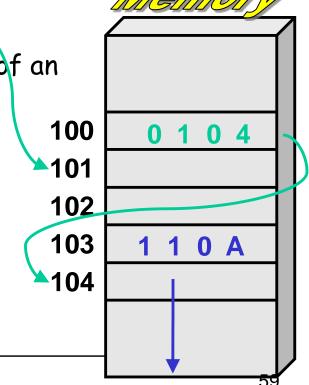

## 7. Relative Addressing Mode

In relative addressing mode, contents of Program Counter PC is added to address part of instruction to obtain effective address.

The address part of the instruction is called as offset and it can +ve or -ve.

When the offset is added to the PC the resultant number is the memory location where the operand will be placed.

X(PC) - note that X is a signed number Branch > 0 LOOP

This location is computed by specifying it as an offset from the current value of PC.

Branch target may be either before or after the branch instruction, the offset is given as a singed num.

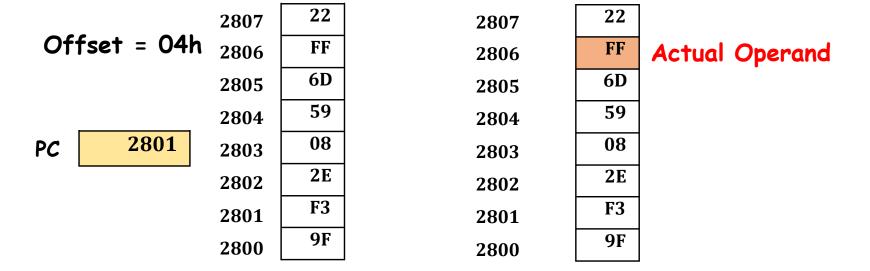

## Ex. Relative Addressing mode

Effective address of operand = PC + O1 + offsetEffective address of operand = 2801 + O1 + O4Effective address of operand = 2806h

# Ex.Relative Addressing

|       |          | 2807 | 22 | 2807 | 22 | Actual Operand |

|-------|----------|------|----|------|----|----------------|

| Offse | et = 03h | 2806 | FF | 2806 | FF |                |

|       |          | 2805 | 6D | 2805 | 6D |                |

|       |          | 2804 | 59 | 2804 | 59 |                |

| PC    | 2803     | 2803 | 08 | 2803 | 08 |                |

| '     |          | 2802 | 2E | 2802 | 2E |                |

|       |          | 2801 | F3 | 2801 | F3 |                |

|       |          | 2800 | 9F | 2800 | 9F |                |

Effective address of operand = PC + O1 + offsetEffective address of operand = 2803 + O1 + O3Effective address of operand = 2807h

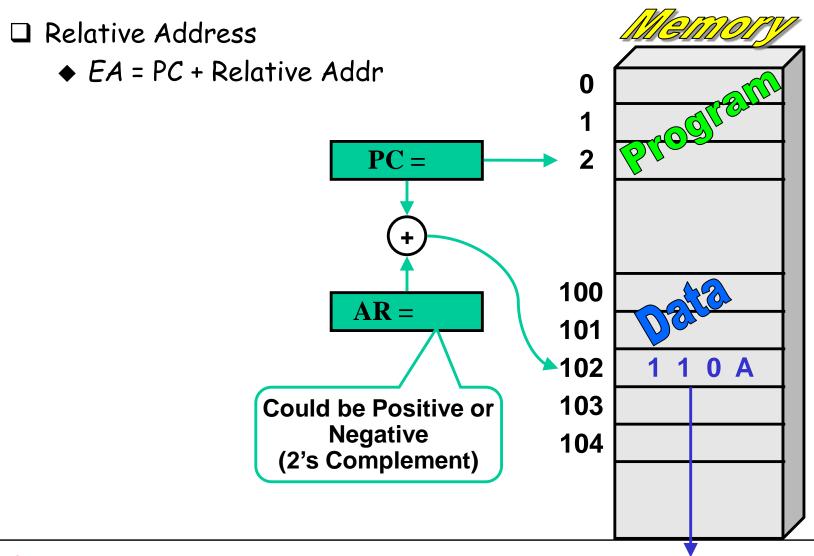

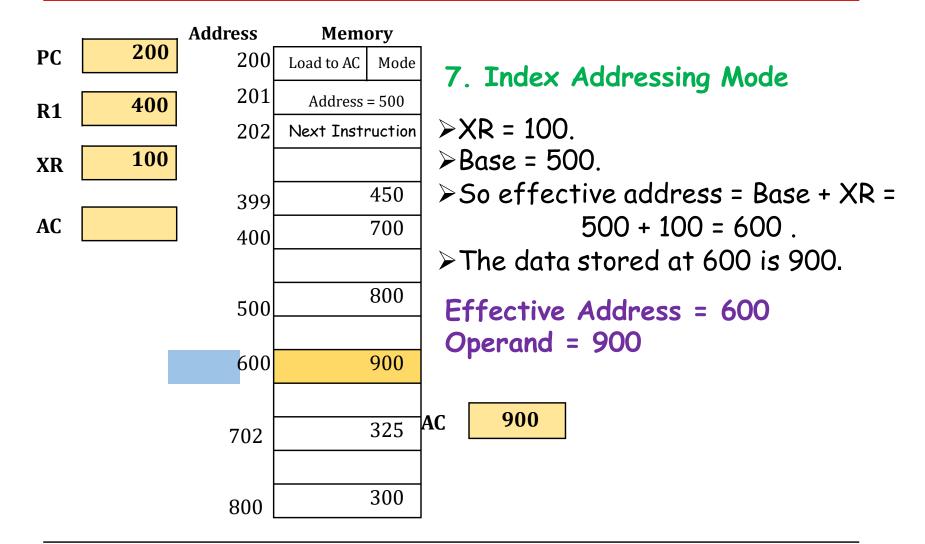

### 8. Indexed Addressing Mode

In index addressing mode, contents of Index register is added to address part of instruction to obtain effective address.

The address part of instruction holds the beginning/base address in the base register.

The index register hold the index value, which is +ve.

Base remains same, the index changes.

When the base is added to the index register the resultant number is the memory location where the operand will be placed.

the effective address of the operand is generated by adding a constant value to the contents of an index register.

$$X(R_i)$$

:  $EA = X + [R_i]$

- The constant X may be given either as an explicit number or as a symbolic name representing a numerical value.

- >If X is shorter than a word, sign-extension is needed.

## Ex. Indexed Addressing Mode

Base = 2800h

0000

Effective address of operand = Base + IX

| 2807 | 22 | 2807 | 22 | 2807 | 22 | 2807 | 22 |

|------|----|------|----|------|----|------|----|

| 2806 | FF | 2806 | FF | 2806 | FF | 2806 | FF |

| 2805 | 6D | 2805 | 6D | 2805 | 6D | 2805 | 6D |

| 2804 | 59 | 2804 | 59 | 2804 | 59 | 2804 | 59 |

| 2803 | 08 | 2803 | 80 | 2803 | 80 | 2803 | 08 |

| 2802 | 2E | 2802 | 2E | 2802 | 2E | 2802 | 2E |

| 2801 | F3 | 2801 | F3 | 2801 | F3 | 2801 | F3 |

| 2800 | 9F | 2800 | 9F | 2800 | 9F | 2800 | 9F |

| IX            | 0000      | IX         | 0001 | IX           | 0002             | IX                       | 0003               |

|---------------|-----------|------------|------|--------------|------------------|--------------------------|--------------------|

| 2800h + 2800h | - 0000h = | 280<br>280 |      | 2800<br>2802 | h + 0002h =<br>h | 2800<br><del>280</del> 3 | 0h + 0003h =<br>3h |

0001

0002

## Ex. Indexed Addressing Mode

Base = 2802h

0000

2802h + 0000h =

IX

2803h

IX

-2802h

Effective address of operand = Base + IX

| 2807 | 22 | 2807 | 22 | 2807 | 22 | 2807 | 22 |

|------|----|------|----|------|----|------|----|

| 2806 | FF | 2806 | FF | 2806 | FF | 2806 | FF |

| 2805 | 6D | 2805 | 6D | 2805 | 6D | 2805 | 6D |

| 2804 | 59 | 2804 | 59 | 2804 | 59 | 2804 | 59 |

| 2803 | 08 | 2803 | 08 | 2803 | 08 | 2803 | 08 |

| 2802 | 2E | 2802 | 2E | 2802 | 2E | 2802 | 2E |

| 2801 | F3 | 2801 | F3 | 2801 | F3 | 2801 | F3 |

| 2800 | 9F | 2800 | 9F | 2800 | 9F | 2800 | 9F |

|      |    |      |    |      |    | •    |    |

IX

0002

2802h + 0002h =

2804h

IX

2805h

0003

2802h + 0003h =

0001

2802h + 0001h =

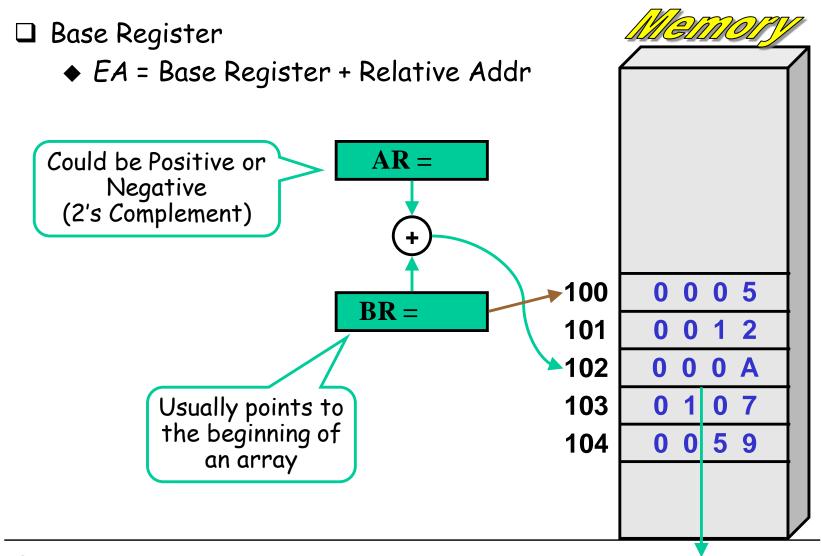

## 9. Base Register Addressing Mode

In base register addressing mode, contents of base register is added to the address part of instruction to obtain effective address.

It is similar to the indexed addressing, contents of base register is added to address part of instruction to obtain effective address

The base register hold the beginning/base address.

The address part of instruction holds the offset.

Offset remains same, the base changes.

When the offset is added to the base register the resultant Number is the Memory location where the operand will be placed.

# Ex. Base Register Addressing

#### Offset= 0001h

Effective address of operand = Base Register + offset

| 2807  | 22       | 2807      | 22        | 2807      | 22        | 2807   | 22          |

|-------|----------|-----------|-----------|-----------|-----------|--------|-------------|

| 2806  | FF       | 2806      | FF        | 2806      | FF        | 2806   | FF          |

| 2805  | 6D       | 2805      | 6D        | 2805      | 6D        | 2805   | 6D          |

| 2804  | 59       | 2804      | 59        | 2804      | 59        | 2804   | 59          |

| 2803  | 08       | 2803      | 08        | 2803      | 08        | 2803   | 08          |

| 2802  | 2E       | 2802      | <b>2E</b> | 2802      | 2E        | 2802   | 2E          |

| 2801  | F3       | 2801      | F3        | 2801      | F3        | 2801   | F3          |

| 2800  | 9F       | 2800      | 9F        | 2800      | 9F        | 2800   | 9F          |

| _     |          |           | 2004      | 1 -       | 2002      | 1 _ [  | 2803        |

| Base  | 2800     | Base      | 2801      | Base      | 2802      | Base   | 2003        |

| 2800l | ı + 0001 | h = 2801h | + 0001h   | a = 2802] | h + 0001h | = 2803 | h + 0001h = |

## Ex. Base Register Addressing

Offset= 0003h

Effective address of operand = Base Register + offset

| 2807 | 22 | 2807 | 22 | 2807 | 22 | 2807 | 22 |

|------|----|------|----|------|----|------|----|

| 2806 | FF | 2806 | FF | 2806 | FF | 2806 | FF |

| 2805 | 6D | 2805 | 6D | 2805 | 6D | 2805 | 6D |

| 2804 | 59 | 2804 | 59 | 2804 | 59 | 2804 | 59 |

| 2803 | 08 | 2803 | 08 | 2803 | 08 | 2803 | 08 |

| 2802 | 2E | 2802 | 2E | 2802 | 2E | 2802 | 2E |

| 2801 | F3 | 2801 | F3 | 2801 | F3 | 2801 | F3 |

| 2800 | 9F | 2800 | 9F | 2800 | 9F | 2800 | 9F |

|      |    | _    |    |      |    |      |    |

**Base**

2800h + 0003h = 2803h

Base

2800

2801h + 0003h = 2804h

Base

2801

2802h + 0003h = 2805h

2802

**Base**

2803h + 0003h = 2806h

2803

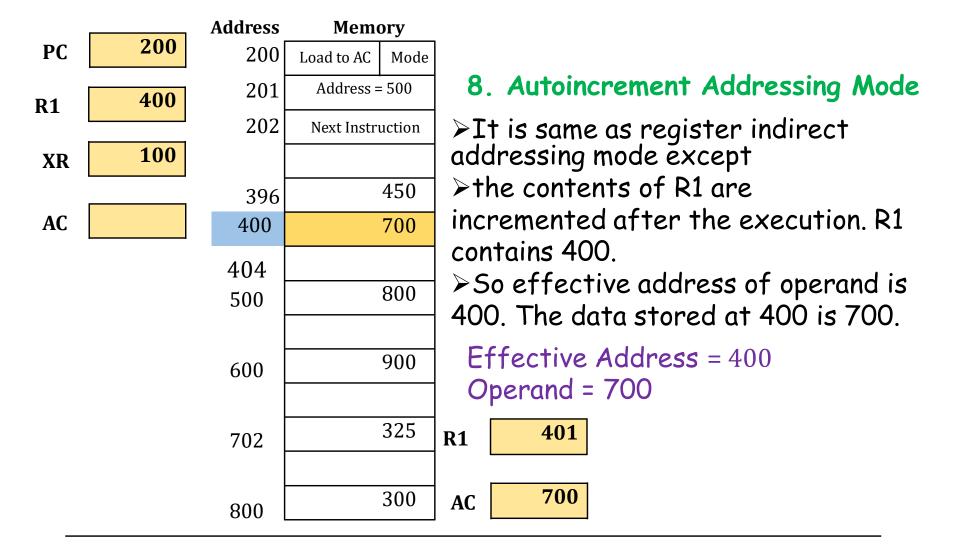

### 10.Additional Modes

- Autoincrement mode the effective address of the operand is the contents of a register specified in the instruction. After accessing the operand, the contents of this register are automatically incremented to point to the next item in a list.

- (R<sub>i</sub>)+. The increment is 1 for byte-sized operands, 2 for 16bit operands, and 4 for 32-bit operands.

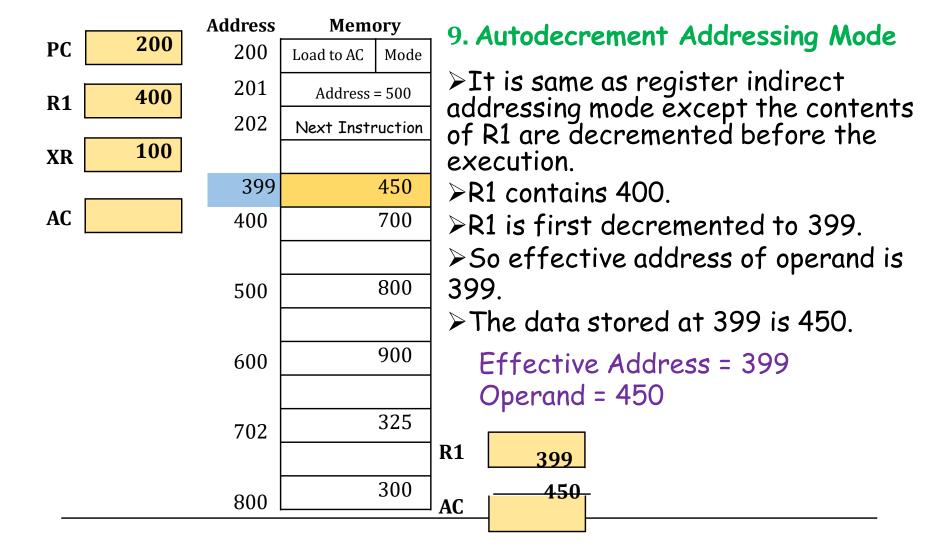

- > Autodecrement mode: -(Ri) decrement first

Figure 2.16. The Autoincrement addressing mode used in the program

## 10(a). Autoincrement Addressing

### HL pair incremented after its value is used

2802 HL **At** start: **22** 22 **22 22** 2807 2807 2807 2807 FF FF FF FF 2806 2806 2806 2806 **6D 6D 6D** 6D 2805 2805 2805 2805 **59 59 59 59** 2804 2804 2804 2804 **80 08** 08 08 2803 2803 2803 2803 **2E 2E 2E 2E** 2802 2802 2802 2802 **F3 F3 F3 F3** 2801 2801 2801 2801 9F 9F 9F 9F 2800 2800 2800 2800 2802 2804 2803 2805 HL HL HL HL 1st 2nd 3rd 4th **Time Time** <del>Time</del> Time

Time

## 10(b). Autodecrement Addressing

### HL pair decremented before its value is used

**Time**

2807 At HL start: **22** 22 **22** 22 2807 2807 2807 2807 FF FF FF FF 2806 2806 2806 2806 **6D 6D 6D 6D** 2805 2805 2805 2805 **59 59 59** 2804 59 2804 2804 2804 **08 08 08** 08 2803 2803 2803 2803 **2E 2E 2E 2E** 2802 2802 2802 2802 **F3 F3 F3 F3** 2801 2801 2801 2801 9F 9F 9F 9F 2800 2800 2800 2800 2804 2806 2805 2807 HL HL HL HL 1st 2nd 3rd 4th

**Time**

Time

# Addressing modes

| Mode               | Assembly                | Register Transfer                         |

|--------------------|-------------------------|-------------------------------------------|

| Direct address     | LD ADR                  | $AC \leftarrow M[ADR]$                    |

| Indirect address   | LD @ADR                 | $AC \leftarrow M[M[ADR]]$                 |

| Immediate operand  | LD # NBR                | AC ← NBR                                  |

| Relative address   | LD \$ADR                | $AC \leftarrow M[PC + ADR]$               |

| Index addressing   | LD ADR(XR)              | $AC \leftarrow M[ADR + XR]$               |

| Base register addr | LD ADR (BR)             | AC←M [ADR+BR]                             |

| Register           | LD R1                   | AC ← R1                                   |

| Register indirect  | LD (R1) / MOV A,<br>@R1 | $AC \leftarrow M[R1]$                     |

| Autoincrement      | LD (R1)+                | $AC \leftarrow M[R1], R1 \leftarrow R1+1$ |

| Autodecrement      | LD -(R1)                | AC← M [R1], R1← R1-1                      |

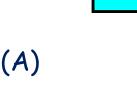

## Addressing Modes-additional

| The                          | Name                       | Assembler syntax       | Addressingfunction                           |

|------------------------------|----------------------------|------------------------|----------------------------------------------|

| ifferent                     | Immediate                  | #Value                 | Operand = Value                              |

| vays in which<br>he location | Register                   | R <i>i</i>             | EA = Ri                                      |

| f an<br>perand is            | Absolute (Direct)          | LOC                    | EA = LOC                                     |

| pecified in<br>n             | Indirect                   | (R <i>i</i> )<br>(LOC) | EA = [Ri]<br>EA = [LOC]                      |

| nstruction<br>re referred    | Index                      | X(R <i>i</i> )         | EA = [Ri] + X                                |

| o as<br>ddressing            | Base with index            | (Ri,Rj)                | $EA = \left[ Ri \right] + \left[ Rj \right]$ |

| nodes.                       | Base with index and offset | X(Ri,Rj)               | EA = [Ri] + [Rj] + X                         |

|                              | Relative                   | X(PC)                  | EA = [PC] + X                                |

|                              | Autoincrement              | (R <i>i</i> )+         | EA = [Ri]; Increment $Ri$                    |

|                              | Autodecrement              | -(R <i>i</i> )         | Decrement Ri;<br>EA = [Ri]                   |

|                              |                            |                        |                                              |

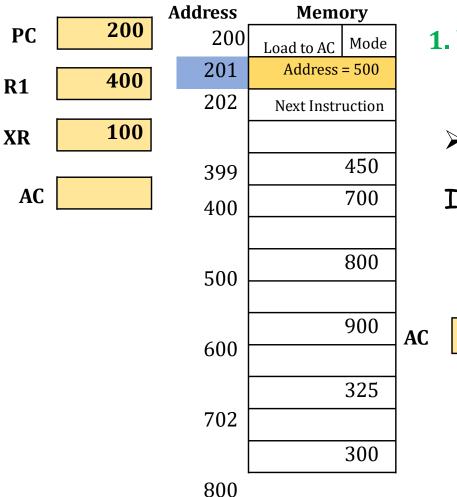

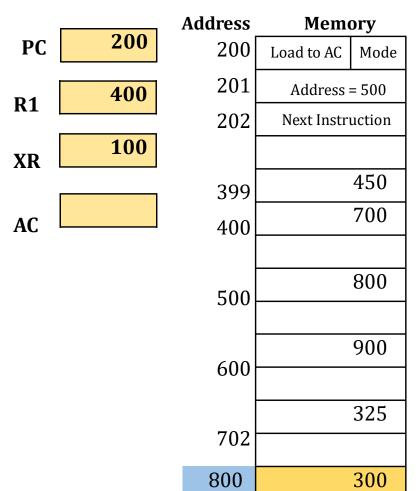

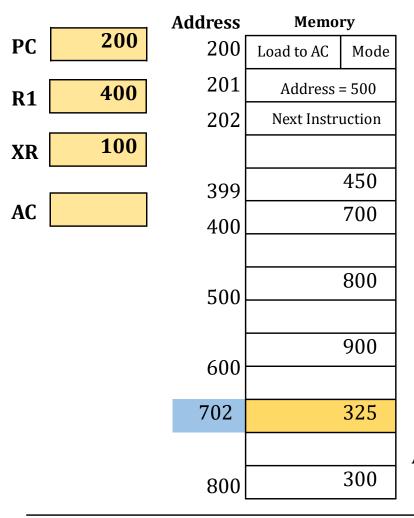

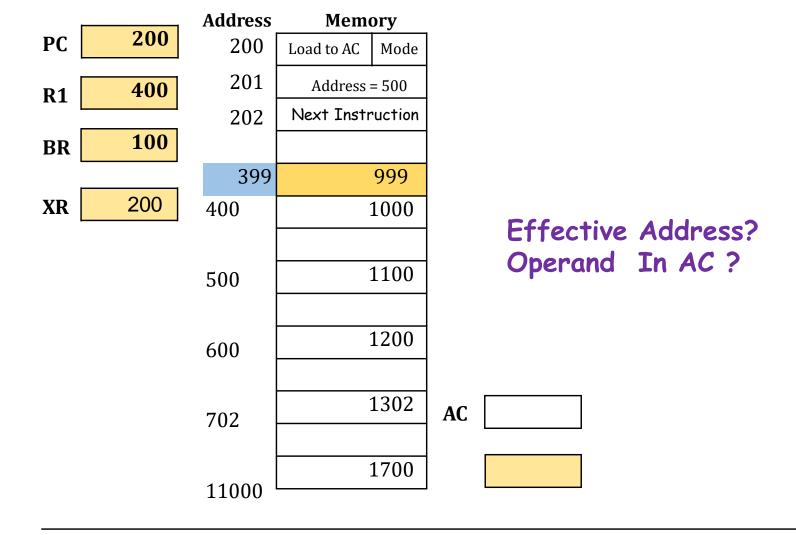

## problem-to find EA of the operand

|     |     | Addres | Memory     |        |

|-----|-----|--------|------------|--------|

| PC  | 200 | s      | Load to AC | Mode   |

| R1  | 400 | 200    | Address    | = 500  |

| 111 |     | 201    | Next Instr | uction |

| XR  | 100 | 202    |            |        |

|     |     | 399    |            | 450    |

| AC  |     | 400    |            | 700    |

|     |     |        |            |        |

|     |     | 500    |            | 800    |

|     |     |        |            |        |

|     |     | 600    |            | 900    |

|     |     |        |            |        |

|     |     | 702    |            | 325    |

|     |     |        |            |        |

|     |     | 800    |            | 300    |

|     |     |        |            | •      |

Find out the effective address of operand and operand value by considering different addressing modes.

- Memory is having first instruction to load AC.

- > Mode will specify the addressing mode to get operand.

- >Address field of instruction is 500.

PC = Program Counter

R1 = Register

XR = Index Register

AC = Accumulator

### Problem-solution-immediate addressing mode

### 1. Immediate Addressing Mode

LDI 500

>As instruction contains immediate number 500. It is stored as address 201.

Operand = 500

Effective Address = 201

C 500

## Problem-solution- reg. mode

|    | 000 | Address | Memo       | ory    |

|----|-----|---------|------------|--------|

| PC | 200 | 200     | Load to AC | Mode   |

| R1 | 400 | 201     | Address :  | = 500  |

|    |     | 202     | Next Instr | uction |

| XR | 100 |         |            |        |

|    |     | 399     |            | 450    |

| AC |     | 400     |            | 700    |

|    |     |         |            |        |

|    |     | 500     |            | 800    |

|    |     |         |            |        |

|    |     | 600     |            | 900    |

|    |     |         |            |        |

|    |     | 702     |            | 325    |

|    |     |         |            |        |

|    |     | 800     |            | 300    |

|    |     |         |            | •      |

### 2. Register Addressing Mode

- Register R1 contains 400.

- As operand is in register so no any memory location.

Effective Address = Nil Operand = 400

# solution -reg indirect mode

Memory

Address

|    |     | Address    | memory           |                                      |

|----|-----|------------|------------------|--------------------------------------|

| PC | 200 | 200        | Load to AC Mode  | 3. Register Indirect Addressing Mode |

| R1 | 400 | 201<br>202 | Address = 500    |                                      |

|    |     | 202        | Next Instruction | ≻Register R1 contains 400.           |

| XR | 100 | 200        |                  | >So effective address of             |

|    |     | 399        | 450              | operand is 400. The data stored      |

| AC |     | 400        | 700              | at 400 is 700.                       |

|    |     |            |                  | Effective Address = 400              |

|    |     | 500        | 800              | Operand = 700                        |

|    |     |            |                  | AC 700                               |

|    |     | 600        | 900              | AC 700                               |

|    |     | 702        | 325              |                                      |

|    |     |            |                  |                                      |

|    |     | 800        | 300              |                                      |

| _  |     | 800        | 300              |                                      |

### solution-direct addressing

|    |     | Address | Memo       | ory    |

|----|-----|---------|------------|--------|

| PC | 200 | 200     | Load to AC | Mode   |

| R1 | 400 | 201     | Address :  | = 500  |

|    |     | 202     | Next Instr | uction |

| XR | 100 |         |            |        |

|    |     | 399     |            | 450    |

| AC |     | 400     |            | 700    |

|    |     |         |            |        |

|    |     | 500     |            | 800    |

|    |     |         |            |        |

|    |     | 600     |            | 900    |

|    |     |         |            |        |

|    |     | 702     |            | 325    |

|    |     |         |            |        |

|    |     | 800     |            | 300    |

### 4. Direct Addressing Mode

Instruction contains the address 500.

So effective address of operand is 500. The data stored at 500 is 800.

Effective Address = 500 Operand = 800

### solution -indirect addressing

### 5. Indirect Addressing Mode

- ➤ Instruction contains the address 500.

- >Address at 500 is 800.

- >So effective address of operand is 800. The data stored at 800 is 300.

Effective Address = 800 Operand = 300

## solution-relative addressing

### 6. Relative Addressing Mode

- >PC = 200.

- >Offset = 500.

- >Instruction is of 2 bytes.

- $\gt$  So effective address = PC + 2 + offset = 200 + 500 +2 = 702.

- The data stored at 702 is 325

Effective Address = 702 Operand = 325

### Problem-solution-index addressing

### solution -autoincrement addressing

### solution-autodecrement addressing

# Complete solution

| Addressing Mode                   | EA  | Operand |

|-----------------------------------|-----|---------|

| Immediate Addressing Mode         | 201 | 500     |

| Register Addressing Mode          | Nil | 400     |

| Register Indirect Addressing Mode | 400 | 700     |

| Direct Addressing Mode            | 500 | 800     |

| Indirect Addressing Mode          | 800 | 300     |

| Relative Addressing Mode          | 702 | 325     |

| Indexed Addressing Mode           | 600 | 900     |

| Autoincrement Addressing Mode     | 400 | 700     |

| Autodecrement Addressing Mode     | 399 | 450     |

## Problem 5- home assignment

Problem5: Consider a 16-bit processor in which the following appears in main memory, starting at location 200:

| 200 | Load to AC       | Mode |  |

|-----|------------------|------|--|

| 201 | 500              |      |  |

| 202 | Next instruction |      |  |

The first part of the first word indicates that this instruction loads a value into an accumulator. The Mode field specifies an addressing mode and, if appropriate, indicates a source register; assuming that when used, the source register is R1, which has a value of 400

There is also a base register that contains the value of 100. the value of 500 in location 201 may be part of the address calculation. Assume that location 399 contains the value 999, location 400 contains the value 1000, and so on. Determine the effective address and the operand to be loaded for the following addressing modes:

### Solution (problem 5)-addressing modes

|   | EA            | Operand | Mode? |

|---|---------------|---------|-------|

| a | 500           | 1100    |       |

| b | 201           | 500     |       |

| С | 1100          | 1700    |       |

| d | 201+1+500=702 | 1302    |       |

| e | 500+100=600   | 1200    |       |

| f | R1            | 400     |       |

| g | 400           | 1000    |       |

| h | 400           | 1000    |       |

Note. Identify the addressing mode and fill the lost column

## Problem 6 -Home assignment

|    | 1000 | Addres Me |                  | mory |  |

|----|------|-----------|------------------|------|--|

| PC | 1000 | s         | Load to AC       | Mode |  |

| R1 | 1000 | 200       | Address = 1000   |      |  |

| ΚI | 2000 | 202       | Next Instruction |      |  |

| XR | 400  | 204       |                  |      |  |

|    |      | 396       |                  | 450  |  |

| AC |      | 400       |                  | 700  |  |

|    |      | 996       |                  |      |  |

|    |      | 1000      |                  | 1800 |  |

|    |      | 1004      |                  |      |  |

|    |      | 1204      |                  | 900  |  |

|    |      | 1400      |                  | 800  |  |

|    |      | 1700      |                  | 325  |  |

|    |      | 1800      |                  | 625  |  |

|    |      | 2000      |                  | 300  |  |

|    |      | •         |                  |      |  |

Addroc

Find out the effective address of operand and operand value by considering different addressing modes.

- The word length of the processor is 4 bytes.

- Memory is having first instruction to load AC.

- > Mode will specify the addressing mode to get operand.

- > Address field of instruction is 1000.

PC = Program Counter

R1 = Register

XR = Index Register

AC = Accumulator

#### Problem 7:

Register R1 and R2 contain values 1800 and 3800 respectively. The word length of the processor is 4 bytes. What is the effective address of the memory operand in each one of the following cases?

- 1) ADD 100 (R2), R6.

- 2) LOAD R6, 20 (R1,R2)

- 3) STORE -(R2), R6

- 4) SUBTRACT (R2)+, R6

### Solution (problem 7)

- 1) Effective address = 100 + Contents of R2 = 100 + 3800 = 3900.

- 2) Effective address = 20 + Contents of R1 + Contents of R2 = 20 + 1800 + 3800 = 5620.

- 3) Effective address = Contents of R2 4 = 3800 4 = 3796.

- 4) Effective address = Contents of R2 = 3800.

Problem: 8

Given the following memory values and a one-ad

dress machine with an

#### accumulator:

- >Word 20 contains 40

- ➤ Word 30 contains 50

- >Word 40 contains 60

- >Word 50 contains 70

- \*What values do the following instructions load into the Accumulator?

- a) Load IMMEDIATE 20

- b) Load DIRECT 20

- c) Load INDIRECT 20

- d) Load IMMEDIATE 30

- e) Load DIRECT 30

- f) Load INDIRECT 30

### Solution(problem 8)

- a) 20

- b) 40

- c) 60

- d)30

- e)50

- f) 70

#### Problem: 9

Let the address stored in the program counter be designated by the symbol X1.

The instruction stored in X1 has an address part (operand reference) X2.

The operand needed to execute the instruction is stored in the memory word with address X3.

An index register contains the value X4.

\*What is the relationship between these various quantities if the addressing mode of the instruction is a) Direct. b) indirect. c) PC relative. d) indexed

Solution: (problem 9)

- a) X3=X2

- b) X3=(X2)

- c) X3=X1+X2+1

- d) X3=X2+X4

Problem: 10

An address field in an instruction contains decimal value 14. Where is the corresponding operand located for:

- a) immediate addressing?

- b) direct addressing?

- c) indirect addressing?

- d) register addressing?

- e) register indirect addressing?

#### Solution (problem 10)

- a) 14 (The address field).

- b) Memory location 14.

- c) The memory location whose address is in memory location 14.

- d) Register 14.

- e) The memory location whose address is in register 14

### Assembly Language

Machine instructions are represented by patterns of 0s and 1s.

Such patterns are awkward to deal with when discussing or preparing programs. Therefore, we use symbolic names to represent the patterns.

EX. Move, Add, Increment, and Branch, for the instruction operations to represent the corresponding binary code patterns.

When writing programs for a specific computer, such words are normally replaced by acronyms called *mnemonics*, such as MOV, ADD, INC, and BR.

Programs written in an assembly language can be automatically translated into a sequence of machine instructions by a program called an assembler.

The assembler program is one of a collection of utility programs that are a part of the system software.

The assembler, like any other program, is stored as a sequence of machine instructions in the memory of the computer.

A user program is usually entered into the computer through a keyboard and stored either in the memory or on a magnetic disk.

The user program is simply a set of lines of alphanumeric characters.

When the assembler program is executed, it reads the user program, analyzes it, and then generates the desired machine language program. The latter contains patterns of 0s and 1s specifying instructions that will be executed by the computer.

The user program in its original alphanumeric text format is called a source program, and the assembled machine language program is called an object program.

### Human-Readable Machine Language

- ☐ Computers understand ones and zeros...

0001110010000110

- ☐ Humans like symbols...

ADD R6,R2,R6 ; increment index reg.

- □ Assembler is a program that turns symbols into machine instructions.

- ◆ ISA-specific: close correspondence between symbols and instruction set

- mnemonics for opcodes

- labels for memory locations

- additional operations for allocating storage and initializing data

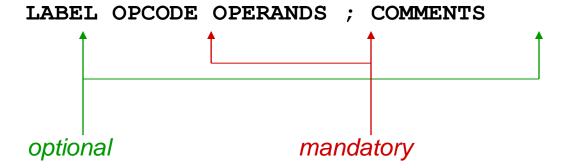

## Assembly Language Syntax

- □ Each line of a program is one of the following:

- ◆ an instruction

- ◆ an assember directive (or pseudo-op) (SUM EQU 200)

- ◆ a comment

- □ Whitespace (between symbols) and case are ignored.

- □ Comments (beginning with ";") are also ignored.

- ☐ An instruction has the following format:

#### Opcodes and Operands

#### Opcodes

- reserved symbols that correspond to instructions

- ex: ADD, AND, LD, LDR, ...

#### Operands

- ◆ registers -- specified by Rn, where n is the register number

- ◆ numbers -- indicated by # (decimal) or x (hex)

- ◆ label -- symbolic name of memory location

- separated by comma

- ◆ number, order, and type correspond to instruction format

- ex:

```

ADD R1,R1,R3

ADD R1,R1,#3

LD R6,NUMBER

BRZ LOOP

```

#### Labels and Comments

#### □ Label

- placed at the beginning of the line

- ◆ assigns a symbolic name to the address corresponding to line

- ex:

```

LOOP ADD R1,R1,#-1

BRp LOOP

```

#### ☐ Comment

- anything after a semicolon is a comment

- ♦ ignored by assembler

- ◆ used by humans to document/understand programs

- ♦ tips for useful comments:

- avoid restating the obvious, as "decrement R1"

- provide additional insight, as in "accumulate product in R6"

- use comments to separate pieces of program

### Assembler Directives

- ☐ Pseudo-operations

- ♦ do not refer to operations executed by program

- ◆ used by assembler

- ♦ look like instruction, but "opcode" starts with dot

| Opcode    | Operand               | Meaning                                                             |

|-----------|-----------------------|---------------------------------------------------------------------|

| .ORIG     | address               | starting address of program                                         |

| . END     |                       | end of program                                                      |

| .BLKW     | n                     | allocate n words of storage                                         |

| .FILL     | n                     | allocate one word, initialize with value n                          |

| . STRINGZ | n-character<br>string | allocate n+1 locations, initialize w/characters and null terminator |

- ☐ Use the following style guidelines to improve the readability and understandability of your programs:

- 1. Provide a program header, with author's name, date, etc., and purpose of program.

- 2. Start labels, opcode, operands, and comments in same column for each line. (Unless entire line is a comment.)

- 3. Use comments to explain what each register does.

- 4. Give explanatory comment for most instructions.

- 5. Use meaningful symbolic names.

- Mixed upper and lower case for readability.

- ASCIItoBinary, InputRoutine, SaveR1

- 6. Provide comments between program sections.

- 7. Each line must fit on the page -- no wraparound or truncations.

- Long statements split in aesthetically pleasing manner.

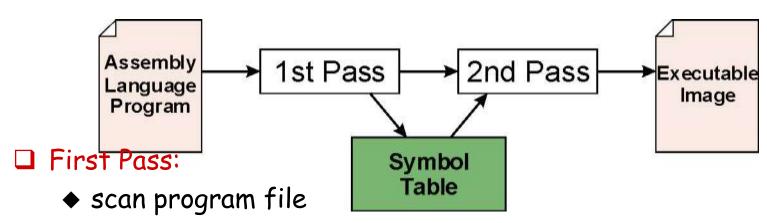

#### Assembly Process

☐ Convert assembly language file (.asm) into an executable file (.obj)

♦ find all labels and calculate the corresponding addresses; this is called the <u>symbol table</u>

#### ☐ Second Pass:

convert instructions to machine language, using information from symbol table

#### First Pass: Constructing the Symbol Table

- 1. Find the .ORIG statement, which tells us the address of the first instruction.

- ◆ Initialize location counter (LC), which keeps track of the current instruction.

- 2. For each non-empty line in the program:

- a) If line contains a label, add label and LC to symbol table.

- b) Increment LC.

- NOTE: If statement is .BLKW or .STRINGZ, increment LC by the number of words allocated.

- 3. Stop when .END statement is reached.

- NOTE: A line that contains only a comment is considered an empty line.

☐ Construct the symbol table

| Symbol | Address |

|--------|---------|

|        |         |

|        |         |

|        |         |

|        |         |

|        |         |

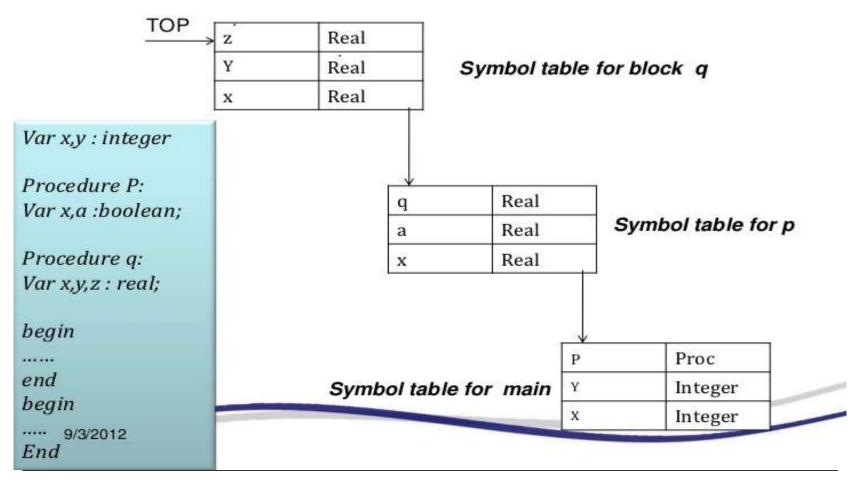

#### SYMBOL TABLE ORGANIZATION

### Second Pass: Generating Machine Language

- ☐ For each executable assembly language statement, generate the corresponding machine language instruction.

- ◆ If operand is a label, look up the address from the symbol table.

- Loading is the process of copying an executable image into memory.

- more sophisticated loaders are able to <u>relocate</u> images to fit into available memory

- ♦ must readjust branch targets, load/store addresses

- ☐ Linking is the process of resolving symbols between independent object files.

- suppose we define a symbol in one module, and want to use it in another

- ◆ some notation, such as .EXTERNAL, is used to tell assembler that a symbol is defined in another module

- ♦ linker will search symbol tables of other modules to resolve symbols and complete code generation before loading

#### Types of Instructions

> Data Transfer Instructions

| Name     | Mnemonic |

|----------|----------|

| Load     | LD       |

| Store    | ST       |

| Move     | MOV      |

| Exchange | XCH      |

| Input    | IN       |

| Output   | OUT      |

| Push     | PUSH     |

| Pop      | POP      |

Data value is not modified

## Data Transfer Instructions

| Mode              | Assembly |        | Register Transfer                         |

|-------------------|----------|--------|-------------------------------------------|

| Direct address    | LD       | ADR    | $AC \leftarrow M[ADR]$                    |

| Indirect address  | LD       | @ADR   | $AC \leftarrow M[M[ADR]]$                 |

| Relative address  | LD       | \$ADR  | $AC \leftarrow M[PC+ADR]$                 |

| Immediate operand | LD       | # NBR  | AC ← NBR                                  |

| Index addressing  | LD       | ADR(X) | $AC \leftarrow M[ADR+XR]$                 |

| Register          | LD       | R1     | $AC \leftarrow R1$                        |

| Register indirect | LD       | (R1)   | $AC \leftarrow M[R1]$                     |

| Autoincrement     | LD       | (R1)+  | $AC \leftarrow M[R1], R1 \leftarrow R1+1$ |

## Data Manipulation Instructions

- > Arithmetic

- > Logical & Bit Manipulation

- > Shift

| Name              | Mnemonic |

|-------------------|----------|

| Clear             | CLR      |

| Complement        | COM      |

| AND               | AND      |

| OR                | OR       |

| Exclusive-OR      | XOR      |

| Clear carry       | CLRC     |

| Set carry         | SETC     |

| Complement carry  | COMC     |

| Enable interrupt  | EI       |

| Disable interrupt | DI       |

# Data Manipulation Instructions

| Name                 | Mnemonic |

|----------------------|----------|

| Increment            | INC      |

| Decrement            | DEC      |

| Add                  | ADD      |

| Subtract             | SUB      |

| Multiply             | MUL      |

| Divide               | DIV      |

| Add with carry       | ADDC     |

| Subtract with borrow | SUBB     |

| Negate               | NEG      |

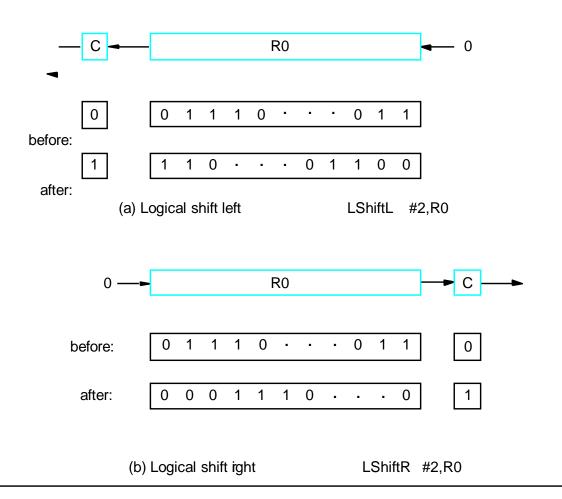

## Data Manipulation Instructions

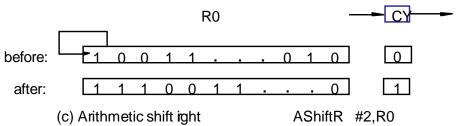

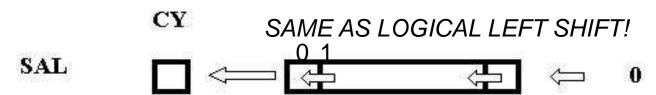

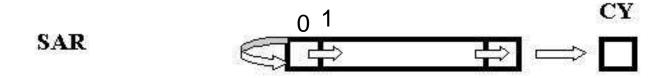

| Name                       | Mnemonic |

|----------------------------|----------|

| Logical shift right        | SHR      |

| Logical shift left         | SHL      |

| Arithmetic shift right     | SHRA     |

| Arithmetic shift left      | SHLA     |

| Rotate right               | ROR      |

| Rotate left                | ROL      |

| Rotate right through carry | RORC     |

| Rotate left through carry  | ROLC     |

# Program Control Instructions

| Name                  | Mnemonic |                       |

|-----------------------|----------|-----------------------|

| Branch                | BR       |                       |

| Jump                  | JMP      |                       |

| Skip                  | SKP      | Subtract A - B but    |

| Call                  | CALL     | don't store the resul |

| Return                | RET      |                       |

| Compare<br>(Subtract) | СМР      | 10110001              |

| Test (AND)            | TST      |                       |

|                       | N        | 00001000<br>lask      |

## Conditional Branch Instructions

| Mnemonic | Branch Condition      | Tested<br>Condition |

|----------|-----------------------|---------------------|

| BZ       | Branch if zero        | Z = 1               |

| BNZ      | Branch if not zero    | Z = 0               |

| BC       | Branch if carry       | <i>C</i> = 1        |

| BNC      | Branch if no carry    | <i>C</i> = 0        |

| BP       | Branch if plus        | S = 0               |

| BM       | Branch if minus       | S = 1               |

| BV       | Branch if overflow    | V = 1               |

| BNV      | Branch if no overflow | V = 0               |

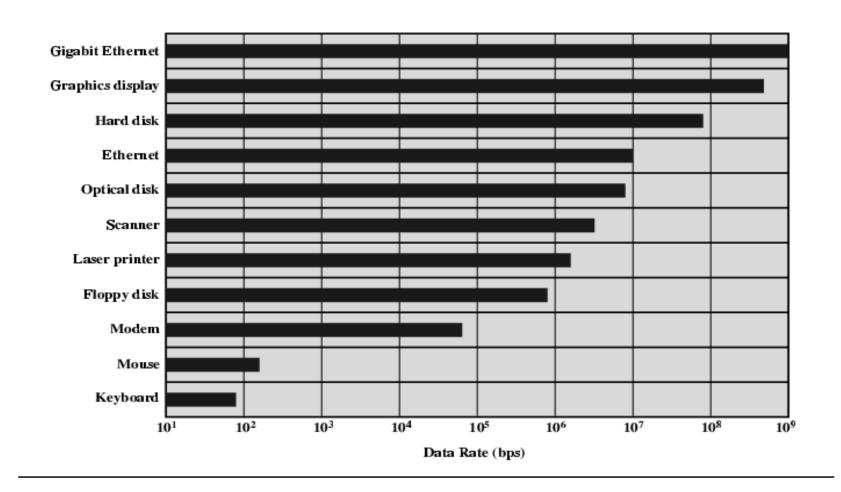

#### Basic Input/output Operations

- > The data on which the instructions operate are not necessarily already stored in memory.

- > Data need to be transferred between processor and outside world (disk, keyboard, etc.)

- > I/O operations are essential, the way they are performed can have a significant effect on the performance of the computer.

- ☐ Human readable

- ◆ Screen, printer, keyboard

- ☐ Machine readable

- ◆ Monitoring and control

- □ Communication

- ◆ Modem

- ◆ Network Interface Card (NIC)

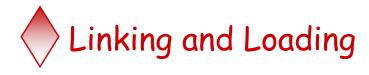

#### Generic Model of I/O Module

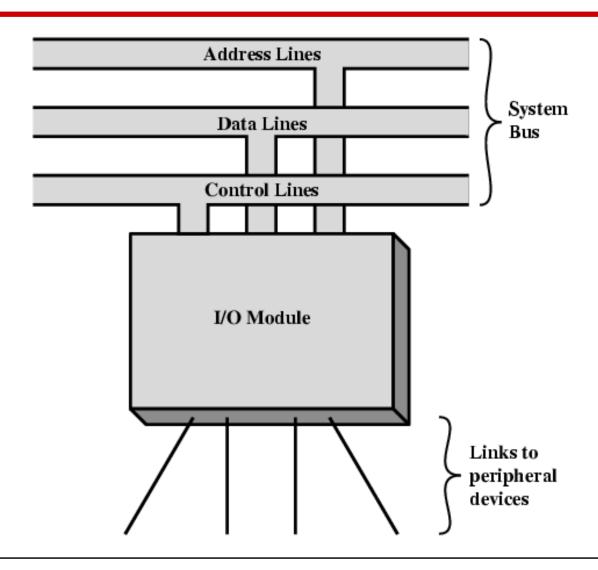

### External Device Block Diagram

# I/O Module Function

- \* Control & Timing

- CPU Communication

- Device Communication

- Data Buffering

- Error Detection

- ❖ CPU checks I/O module device status

- ❖ I/O module returns status

- If ready, CPU requests data transfer

- ❖ I/O module gets data from device

- ❖ I/O module transfers data to CPU

- Variations for output, DMA, etc.

## Input Output Techniques

- Programmed

- Interrupt driven

- Direct Memory Access (DMA)

- CPU has direct control over I/O

- ♦ Sensing status

- ◆ Read/write commands

- ◆ Transferring data

- ❖ CPU waits for I/O module to complete operation

- ❖ Wastes CPU time

#### Programmed I/O - detail

- CPU requests I/O operation

- ❖ I/O module performs operation

- ❖ I/O module sets status bits

- CPU checks status bits periodically

- ❖ I/O module does not inform CPU directly

- ❖ I/O module does not interrupt CPU

- CPU may wait or come back later

#### Program-Controlled I/O Example

- > Read in character input from a keyboard and produce character output on a display screen.

- > Rate of data transfer (keyboard, display, processor)

- > Difference in speed between processor and I/O device creates the need for mechanisms to synchronize the transfer of data.

- A solution: on output, the processor sends the first character and then waits for a signal from the display that the character has been received. It then sends the second character. Input is sent from the keyboard in a similar way.

- On Input, the processor waits for a signal indicating that a character key has been struck and that its code is available in some buffer register associated with the keyboard. Then the processor proceeds to read that code.

- ☐ Under programmed I/O data transfer is very like memory access (CPU viewpoint)

- □ Each device given unique identifier

- □ CPU commands contain identifier (address)

Status register

Status register

- Registers

- Flags (status register)

- Device interface

difference in speed between the processor and I/O devices creates the need for mechanisms to synchronize the transfer of data between them.

A solution to this problem is as follows; On output, the processor sends the first character and then waits for a signal from the display that the character has been received. It then sends the second character, and so on. Input is sent from the keyboard in a similar way; the processor waits for a signal indicating that a character key has been struck and that its code is available in some buffer register associated with the keyboard. Then the processor proceeds to read that code.

The keyboard and the display are separate devices as shown in Figure .

The action of striking a key on the key board does not automatically cause the corresponding character to be displayed on the screen.

One block of instructions in the I/O program transfers the character into the processor, and another associated block of instructions causes the character to be displayed.

#### Moving a character code from the keyboard to the processor.

- >Striking a key stores the corresponding character code in an 8-bit buffer register associated with the keyboard.

- >Let us call this register DATAIN, as shown in Figure.

- >To inform the processor that a valid character is in DATAIN, a status control flag, SIN, is set to 1.

- >A program monitors SIN, and when SIN is set to 1, the processor reads the contents of DATAIN.

- >When the character is transferred to the processor, SIN is automatically cleared to 0.

- >If a second character is entered at the keyboard, SIN is again set to 1 and the process repeats.

#### Characters transfer from the processor to the display

A buffer register, DATAOUT, and a status control flag, SOUT, are used for this transfer.

When SOUT equals 1, the display is ready to receive a character. Under program control, the processor monitors SOUT, and when SOUT is set to 1, the processor transfers a character code to DATAOUT.

The transfer of a character to DATAOUT clears SOUT to 0. If the display device is ready to receive a second character, SOUT is again set to 1.

The buffer registers DATAIN and DATAOUT and the status flags SIN and SOUT are part of circuitry commonly known as a device interface.

The circuitry for each device is connected to the processor via a bus.

#### Sequence of operations is used for transferring input to processor

In order to perform I/O transfers, we need machine instructions that can check the state of the status flags and transfer data between the processor and the I/O device.

These instructions are similar in format to those used for moving data between the processor and the memory.

For example, the processor can monitor the keyboard status flag SIN and transfer a character from DATAIN to register R1 by the following sequence of operations:

**READWAIT** Branch to **READWAIT** if **SIN** = 0 Input from **DATAIN** to R1

#### Sequence of operations for transferring output to the display

The Branch operation is usually implemented by two machine instructions.

The first instruction tests the status flag and the second performs the branch.

Although the details vary from computer to computer, the main idea is that the processor monitors the status flag by executing a short wait loop and proceeds to transfer the input data when SIN is set to 1 as a result of a key being struck.

The Input operation resets SIN to 0.

An analogous sequence of operations is used for transferring output to the display.

An example is

WRTTEWAIT Branch to WRITEWATT if SOUT = 0

Output from R1 to DATAOUT

Again, the Branch operation is normally implemented by two machine instructions.

- >The wait loop is executed repeatedly until the status flag SOUT is set to 1 by the display when it is free to receive a character.

- The Output operation transfers a character from R1 to DATAOUT to be displayed, and it clears SOUT to 0.

We assume that the initial state of SIN is 0 and the initial state of SOUT is 1.

This initialization is normally performed by the device control circuits when the devices are placed under computer control before program execution begins.

Until now, we have assumed that the addresses issued by the processor to access instructions and operands always refer to memory locations. Many computers use an arrangement called memory-mapped I/O in which some memory address values are used to refer to peripheral device buffer registers, such as DATAIN and DATAOUT.

Thus, no special instructions are needed to access the contents of these registers; data can be transferred between these registers and the processor using instructions that we have already discussed, such as Move, Load, or Store.

For example, the contents of the keyboard character buffer DATAIN can be transferred to register R1 in the processor by the instruction

MoveByte DATAIN,R1

Similarly, the contents ofregister R1 can be transferred to DATAOUT by the instruction

MoveByte RI, DATAOUT

The status flags SIN and SOUT are automatically cleared when the buffer registers DATAIN and DATAOUT are referenced, respectively.

The MoveByte operation code signifies that the operand size is a byte, to distinguish it from the operation code Move that has been used for word operands.

the two data buffets in Figure may be addressed as if they were two memory locations.

It is possible to deal with the status flags SIN and SOUT in the same way, by assigning them distinct addresses.

However, it is more common to include SIN and SOUT in device status registers, one for each of the two devices.

Let us assume that bit in registers INSTATUS and OUTSTATUS corresponds to SIN and SOUT, respectively.

The read Operation just described may now be implemented by the machine instruction sequence

READWAIT Testbit #3,INSTATUS

Branch=0 READWAIT

MoveByte DATAIN,R1

The write operation may be implemented as

WRITEWAIT Testbit #3.0UTSTATUS

Branch=0 WRITEWAIT

MoveByte R1, DATAOUT

The Test bit instruction tests the state of one bit in the destination location, where the bit position to be tested is indicated by the first operand.

If the bit tested is equal to 0, then the condition of the branch instruction is true, and a branch is made to the beginning of the wait loop.

When the device is ready, that is, when the bit tested becomes equal to 1, the data are read from the input buffer or written into the output buffer.

The program shown ,uses these two operations to read a line of characters typed at a keyboard and send them out to a display device.

As the characters are read in, one by one, they are stored in a data area in the memory and then echoed back to display,

|      | Move                             | #LOC,RO                            | Initialize pointer register RO to point to the address of the first location in memory where the characters are to be stored.                         |

|------|----------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| READ | TestBit<br>Braiich=0<br>MoveByte | #3,INSTATUS<br>READ<br>DATAIN,(RO) | Wait for a character to be entered<br>in the keyboard buffer DATAIN.<br>TYansfer the character from DATAIN into<br>the memory (this clears SIN to 0). |

| ЕСНО | TestBit<br>Branch=0              | #3,OUTSTATUS<br>ECHO               | Wait for the display to become ready.                                                                                                                 |

|      | MoveByte                         | (RO),DATAOUT                       | Move the character just read to the display<br>buffer register (this clears SOUT to 0).                                                               |

|      | Compare                          | #CR,(RO)+                          | Check if the character just read is CR<br>(carriage return). If it is not CR, then                                                                    |

|      | Branch/O                         | READ                               | branch back and read another character.                                                                                                               |

|      |                                  |                                    | Also, increment the pointer to store the next character.                                                                                              |

The program finishes when the carriage return character, CR, is read, stored, and sent to the display.

The address of the first byte location of the memory data area where the line is to be stored is LOC.

Register RO is used to point to this area, and it is initially loaded with the address LOC by the first instruction in the program.

RO is incremented for each character read and displayed by the Auto increment addressing mode used in the Compare instruction.

Program -controlled I/O requires continuous involvement of the processor in the I/O activities. Almost all of the execution time for the program is accounted for in the two wait loops, while the processor waits for a character to be struck or for the display to become available.

It is desirable to avoid wasting processor execution time in this situation.

Other I/O techniques, based on the use of interrupts, may be used to improve the utilization of the processor.

Machine instructions that can check the state of the status flags and transfer data: READWAIT Branch to READWAIT if SIN = 0 Input from DATAIN to R1

WRITEWAIT Branch to WRITEWAIT if SOUT = 0

Output from R1 to DATAOUT

Memory-Mapped I/O - some memory address values are used to refer to peripheral device buffer registers. No special instructions are needed. Also use device status registers.

READWAIT Testbit #3, INSTATUS

Branch=0 READWAIT

MoveByte DATAIN, R1

- > Assumption the initial state of SIN is 0 and the initial state of SOUT is 1.

- > Any drawback of this mechanism in terms of efficiency?

- > Two wait loops > processor execution time is wasted

- Alternate solution?

- > Interrupt

#### ☐ Memory mapped I/O

- ◆ Devices and memory share an address space

- ◆ I/O looks just like memory read/write

- ◆ No special commands for I/O

- Large selection of memory access commands available

#### ☐ Isolated I/O

- ♦ Separate address spaces

- ◆ Need I/O or memory select lines

- ◆ Special commands for I/O

- Limited set

- ☐ CPU issues address

- ◆ Identifies module (& device if >1 per module)

- □ CPU issues command

- ◆ Control telling module what to do

- e.g. spin up disk

- ◆ Test check status

- e.g. power? Error?

- ◆ Read/Write

- Module transfers data via buffer from/to device

- > Assumption the initial state of SIN is 0 and the initial state of SOUT is 1.

- > Any drawback of this mechanism in terms of efficiency?

- > Two wait loops -> processor execution time is wasted